# HD6345/HD6445 -CRTC-II(CRT Controller)

The HD6345/HD6445 CRTC-II provides an interface between MPU and a raster scan CRT display. The HD6345 is upward-compatible with the NMOS CRTC HD6845S in pin and software, and has a 68 system bus interface. The HD6445 has a 80 system bus interface. A power dissipation is lowered by adopting the CMOS process.

The CRTC-II offers a variety of functions under MPU control, such as programmable timing signal outputs for CRT monitor and display screen control operation. It can be widely applied to the various types of CRT display systems.

## FEATURES

FLEXIBLE SCREEN FORMAT

- Programmable numbers of characters per screen and rasters per character row

- Programmable horizontal/vertical sync signals and display timing signals

- Up to 16k words refresh memory (14-bit) addressable

- Programmable raster scanning modes: Non-Interlace, Interlace sync, or Interlace sync and video modes

- Up to 256 character rows per field

- High-speed display operation at 4.5 MHz character clock

- Double-size vertical display by raster interpolation

#### VERSATILE DISPLAY FUNCTIONS

- Screen split (max. 4 screens configurable, horizontally)

- Paging and scrolling for each screen

- Smooth scrolling

- Two cursors with programmable width

- Programmable refresh memoly width

#### FACILITATED SYSTEM CONFIGURATION

- 68 system bus interface (HD6345)

- 80 system bus interface (HD6445)

- Three-state control of memory address and raster address

- External synchronization in Master-slave or TV syne modes

- Interrupt request by vertical blanking or light pen strobe detection

- Programmable timing signal for dual-port RAM in MPRAM mode

PIN AND SOFTWARE UPWARD-COMPAT-IBLE WITH HD6845S

SINGLE-5V POWER SUPPLY

CMOS PROCESS

OPERATING TEMPERATURE SPECIFICA-TIONS

- Normal  $-20^{\circ}C \sim +75^{\circ}C$

- J Version  $-40^{\circ}C \sim +85^{\circ}C$

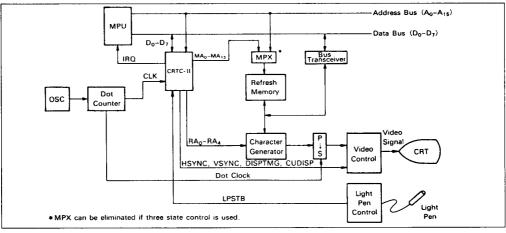

# SYSTEM BLOCK DIAGRAM

# () HITACHI

42 Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

This Material Copyrighted By Its Respective Manufacturer

# **TYPE OF PRODUCTS**

|                      |                            |            | Bus     |                 | CRT Display   |

|----------------------|----------------------------|------------|---------|-----------------|---------------|

| <b>Specification</b> | <b>Bus Interface</b>       | Туре No.   | Timing  | Package         | Timing        |

| Normal               | 6800 system                | HD6345P    | 1.0 MHz | DP-40 (40 pin   | 4.5 MHz (max) |

|                      | Bus interface              | HD63A45P   | 1.5 MHz | plastic Dip)    |               |

|                      |                            | HD63B45P   | 2.0 MHz | -               |               |

|                      |                            | HD6345CP   | 1.0 MHz | CP-44           | -             |

|                      |                            | HD63A45CP  | 1.5 MHz | - (44 pin PLCC) |               |

|                      |                            | HD63B45CP  | 2.0 MHz | _               |               |

|                      | 80 system                  | HD6445P4   | 4.0 MHz | DP-40           | -             |

|                      | Bus interface              | HD6445CP4  |         | CP-44           | _             |

| J version            | 6800 system                | HD6345CPJ  | 1.0 MHz | CP-44           | 4.5 MHz (max) |

| (wide tempera-       | Bus interface              | HD63A45CPJ | 1.5 MHz | -               |               |

| ture range)          |                            | HD63B45CPJ | 2.0 MHz | -               |               |

|                      | 80 system<br>Bus interface | HD6445CP4J | 4.0 MHz | _               |               |

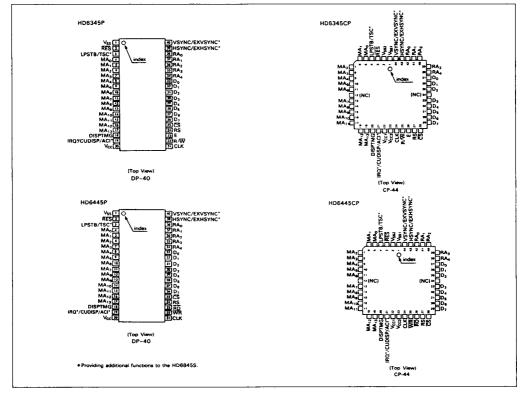

# **PIN ARRANGEMENT**

### **PIN FUNCTION**

| F     | Pin No.         | _                                                        |                                 |                  |                                                                                                                                                                                                                                                                                                                                                                                                                |

|-------|-----------------|----------------------------------------------------------|---------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DP-40 | CP-44           | Symbol                                                   | Pin Name                        | Input/<br>Output | Functions                                                                                                                                                                                                                                                                                                                                                                                                      |

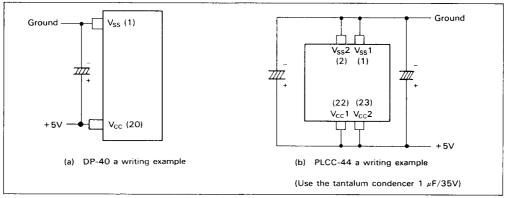

| 1     | 1, 2            | V <sub>SS</sub> (V <sub>SS1</sub> , V <sub>SS2</sub> )** | V <sub>SS</sub>                 | -                | Ground (GND) pin                                                                                                                                                                                                                                                                                                                                                                                               |

| 2     | 3               | RES                                                      | Reset                           | Input            | <ul> <li>Performs external reset on CRTC-II RES assertion causes CRTC-II:</li> <li>(1) Clear all the internal counters</li> <li>(2) Set all the output signals at "L" (D<sub>0</sub>-D<sub>7</sub> are excluded.)</li> <li>(3) Clear registers R30 (Control 1), R31 (Control 2/Status), and R32 (Control 3) (Other registers are not affected at all)</li> <li>RES is valid only while LPSTB is "L"</li> </ul> |

| 3     | 4               | LPSTB                                                    | Light Pen Strobe                | Input            | Informs light pen strobe pulse detection                                                                                                                                                                                                                                                                                                                                                                       |

|       |                 | TSC                                                      | Three State Control             | Input            | Performs three-state control on memory and raster addresses                                                                                                                                                                                                                                                                                                                                                    |

| 4–17  | 5–11,<br>13–19  | MA <sub>0</sub> -MA <sub>13</sub>                        | Memory Address<br>0-13          | Output           | Supplies memory address for periodical<br>memory refresh                                                                                                                                                                                                                                                                                                                                                       |

| 18    | 20              | DISPTMG                                                  | Display Timing                  | Output           | Indicates a screen display period                                                                                                                                                                                                                                                                                                                                                                              |

| 19    | 21              | CUDISP                                                   | Cursor Display                  | Output           | Display cursor on a screen Enabled during<br>DISPTMG is "H"                                                                                                                                                                                                                                                                                                                                                    |

|       |                 | ACI                                                      | Access Inhibit                  | Output           | Supplies MPRAM access inhibit timing<br>(programmable)                                                                                                                                                                                                                                                                                                                                                         |

|       |                 | IRQ                                                      | Interrupt Request               | Output           | Indicates interrupt request to MPU Enabled<br>during DISPTMG is "L"                                                                                                                                                                                                                                                                                                                                            |

| 20    | 22, 23          | V <sub>CC</sub> (V <sub>CC1</sub> , V <sub>CC2</sub> )** | V <sub>CC</sub>                 | -                | Power supply (+5V) pin                                                                                                                                                                                                                                                                                                                                                                                         |

| 21    | 24              | CLK                                                      | V <sub>CC</sub> Character Clock | Input            | Receives character clock timing                                                                                                                                                                                                                                                                                                                                                                                |

| 22    | 25              | R/Ŵ                                                      | Read/Write                      | Input            | Controls data transfer direction between MPU<br>and CRTC-II                                                                                                                                                                                                                                                                                                                                                    |

|       |                 | WR*                                                      | Write                           | Input            | Inputs write signal from MPU                                                                                                                                                                                                                                                                                                                                                                                   |

| 23    | 26              | E                                                        | Enable                          | Input            | Enables register read/write strobe signals<br>from MPU                                                                                                                                                                                                                                                                                                                                                         |

|       |                 | RD*                                                      | Read                            | Input            | Inputs read signal from MPU                                                                                                                                                                                                                                                                                                                                                                                    |

| 24    | 27              | RS                                                       | Register Select                 | Input            | Selects either of address register or other<br>registers Address reg. selected when at "L",<br>and others at "H" Normally, requested to<br>connect to "A <sub>0</sub> " of MPU address bus                                                                                                                                                                                                                     |

| 25    | 28              | <u>CS</u>                                                | Chip Select                     | Input            | Performs addressing on CRTC-II MPU Read/ write upon CRTC-II registers enabled when $\overline{CS}$ is ''L''                                                                                                                                                                                                                                                                                                    |

| 33-26 | 37–35,<br>33–29 | D <sub>0</sub> –D <sub>7</sub>                           | Data Bus 0-7                    | Input/<br>Output | Bidirectional bus for data transfer between MPU and CRTC-II                                                                                                                                                                                                                                                                                                                                                    |

| 38-34 | 42-38           | RA <sub>0</sub> −RA₄                                     | Raster Address 0-4              | Output           | Supplies raster address for selecting raster on<br>character generator                                                                                                                                                                                                                                                                                                                                         |

| 39    | 43              | HSYNC                                                    | Horizontal Sync                 | Output           | Supplies horizontal sync signal                                                                                                                                                                                                                                                                                                                                                                                |

|       |                 | EXHSYNC                                                  | External Horizontal<br>Sync     | Input            | Receives external horizontal sync signal                                                                                                                                                                                                                                                                                                                                                                       |

| 40    | 44              | VSYNC                                                    | Vertical Sync                   | Output           | Supplies vertical sync signal                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                 | EXVSYNC                                                  | External Vertical Sync          | Input            | Receives external vertical sync signal                                                                                                                                                                                                                                                                                                                                                                         |

\*Notes: \*Marked pins are of the HD6445. \*Marked pins are of the CP-44

# **O HITACHI**

# FUNCTION TABLE

| ltem                            | Descriptions                                                                                                                                                                          | Remarks                                                                                                                 |  |

|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|--|

| Programmable<br>Screen Format   | Horizontal scan cycle<br>Vertical scan cycle (by row)<br>Vertical scan cycle (Adjust)<br>Number of displayed chars./row<br>Number of char. rows/screen<br>Number of rasters/char. row | Programmable by char. clock time<br>Programmable by char. row time<br>Programmable by raster time                       |  |

|                                 | Horizontal display position<br>Vertical display position<br>Vertical sync position (Adjust)<br>HSYNC pulse width<br>VSYNC pulse width                                                 | Enabled by programming sync signal<br>output timings<br>Programmable by raster time                                     |  |

| <u> </u>                        | DISPTMG skew                                                                                                                                                                          | 1 or 2 character skew                                                                                                   |  |

| Screen Split                    | 4 split-screens start positions                                                                                                                                                       | Discretely programmable (Unit: row)                                                                                     |  |

|                                 | programmable                                                                                                                                                                          | 2/3/4 screens format selectable                                                                                         |  |

| Cursor Control                  | Cursor display position<br>Cursor height                                                                                                                                              | Two 14-bit cursor registers<br>1 or 2 cursors displayed<br>Display start/end rasters program-                           |  |

|                                 | Cursor width<br>Cursor blink<br>Simultaneous output of 2 cursors<br>(Only 1 availble in MPRAM mode)                                                                                   | mable within a row<br>Programmable by char. clock time<br>1/16 or 1/32 field rate selectable<br>Discretely programmable |  |

|                                 | Cursor display mode<br>CUDISP skew                                                                                                                                                    | OR/EOR mode selectable<br>1 or 2 character skew                                                                         |  |

| Raster Scan<br>Mode             | Non-Interlace mode<br>Interlace sync mode<br>Interlace sync and video mode                                                                                                            | Either one of three modes selectable                                                                                    |  |

| Memory Format                   | Memory width set                                                                                                                                                                      | Memory width programmable wider                                                                                         |  |

|                                 |                                                                                                                                                                                       | than display width (Unit: char.)                                                                                        |  |

| Smooth<br>Scrolling             | Display start raster address set<br>Target screen set                                                                                                                                 | Programmable by char. clock time<br>Any screen selectable                                                               |  |

| Raster<br>Interpolation         | Double-size vertical display<br>Vertical scan cycle doubled                                                                                                                           | Same raster address supplied twice                                                                                      |  |

| External<br>Synchronization     | Synchronization with external sync signals                                                                                                                                            | Superimposed display enhabled on<br>other CRT or TV screens                                                             |  |

| Interrput<br>Request            | Interrupt request signal caused by<br>vertical ratrace period or light pen<br>detection (Disabled in MPRAM mode)                                                                      | Interrupt regest mode programmable                                                                                      |  |

| Light Pen                       | 14-bit Light pen register<br>Light pen raster register                                                                                                                                | Light pen raster address detected                                                                                       |  |

| Refresh<br>Memory<br>Addressing | 14-bit refresh memory address output<br>Four 14-bit screen start address regs.<br>(Display start address programmable                                                                 | Up to 16k words refresh memory<br>accessible<br>Paging and scrolling enabled each                                       |  |

| Three-State                     | for each screen)                                                                                                                                                                      | Screen                                                                                                                  |  |

| Control                         | Three-state control on MA and RA                                                                                                                                                      | Controlled by TSC pin input                                                                                             |  |

| Programmable                    | Programmable timing signal supplied                                                                                                                                                   | In MPRAM mode                                                                                                           |  |

| Timing Output                   | from access inhibit pin                                                                                                                                                               |                                                                                                                         |  |

## CRTC-II NEWLY ADOPTED FEATURES

- 1. Screen Partition (horizontally split into 4 screens)

- 2. Smooth Scrolling

- 3. External Synchronization

- 4. Interrupt request

- 5. Raster Interpolation

- 6. Sync Position Adjustment

- 7. Light Pen Raster Address

- 8. Second Cursor

- 9. Display Momory Width Setting

- 10. 256 Rows Max

- 11. Timing Signal for MPRAM

- 12. Three-state Control of MA/RA Output

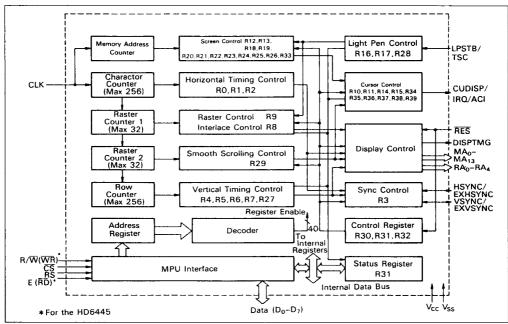

## **INTERNAL BLOCK DIAGRAM**

#### FUNCTIONAL DESCRIPTION

#### PROGRAMMABLE SCREEN FORMAT

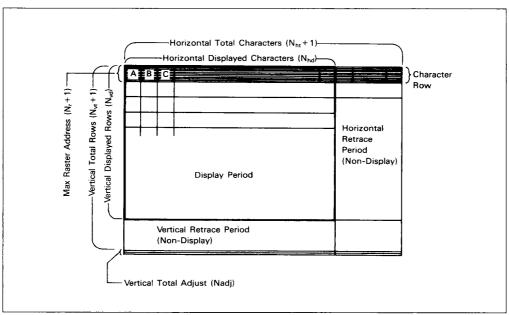

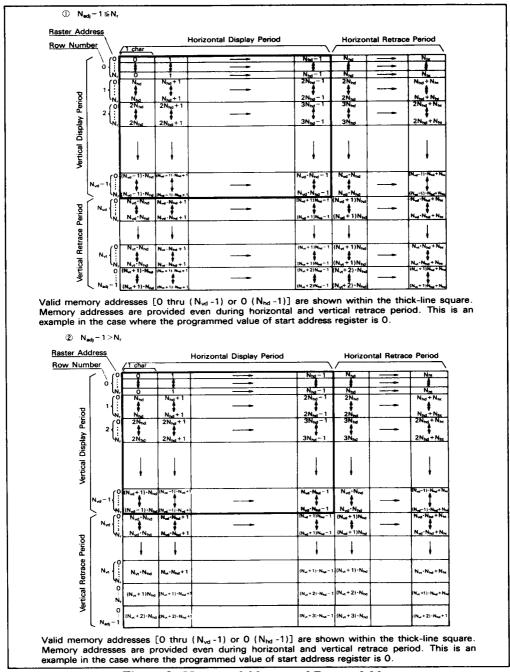

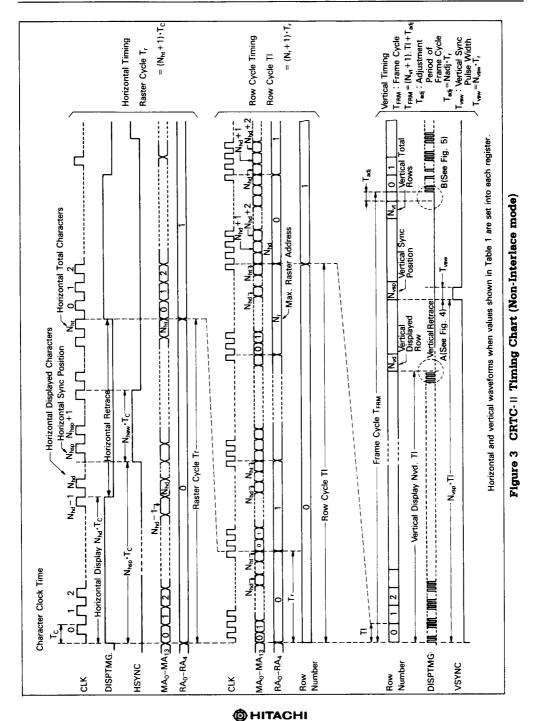

Figure 1 illustrates the screen format example, in Non-Interlace mode, when programming CRTC-II registers as listed in Tabel 1. Figure 2 shows the relation between memory address  $(MA_0-MA_{13})$ , raster address  $(RA_0-RA_4)$  and the location on the CRT screen.

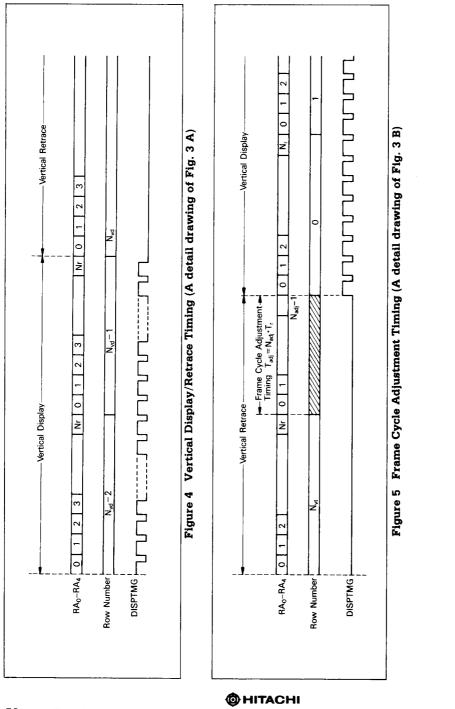

The timing charts of CRT interface signals are shown in Figure 3, and those details are partially shown in Figure 4 and 5.

#### O HITACHI

|                 | register                           |                      |

|-----------------|------------------------------------|----------------------|

| Register<br>No. | Register Name                      | Programmed<br>Values |

| RO              | HORIZONTAL TOTAL<br>CHARACTERS     | Nht                  |

| R1              | HORIZONTAL DISPLAYED<br>CHARACTERS | Nhd                  |

| R2              | HORIZONTAL SYNC<br>POSITION        | Nhsp                 |

| R3              | SYNC WIDTH                         | Nvsw, Nhsw           |

| R4              | VERTICAL TOTAL ROWS                | Nvt                  |

| R5              | VERTICAL TOTAL ADJUST              | Nadj                 |

| R6              | VERTICAL DISPLAYED<br>ROWS         | Nvd                  |

| R7              | VERTICAL SYNC POSITION             | Nvsp                 |

| R9              | MAX. RASTER ADDRESS                | Nr                   |

| R12             | SCREEN 1 START<br>ADDRESS (H)      | 0                    |

| R13             | SCREEN 1 START<br>ADDRESS (L)      | 0                    |

| R30             | CONTROL 1                          | 0                    |

| R31             | CONTROL 2/STATUS                   | 0                    |

| R32             | CONTROL 3                          | 0                    |

#### Tabel 1 Programmed Values in Each Register

# Figure 1 CRT Screen Format

### HITACHI

Figure 2 Memory Address and Raster Address

### HITACHI

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

# HD6345/HD6445

2

49

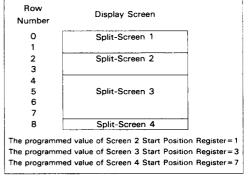

#### SCREEN SPLIT

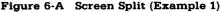

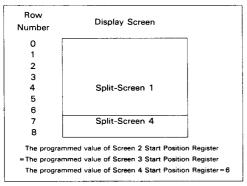

A display screen can be divided into up to four parts in the horizontal direction. Divided four parts are defined as split-screen 1, splitscreen 2, split-screen 3, and split-screen 4.

The starting positions of each split-screen are determined in the number of character row. Split-screen 1 is the base screen, and always starts at row 0, while the other three splitscreens start at any row except row 0. Paging or scrolling (by character) is performed in each split-screen independently. Screen split is controlled by the SP0 and the Sp1 bits of the control 1 register (R30) and the screen start position registers (R18, R21, R24). If the same value is programmed in more than one screen start position register or a start position which is out of display row is programmed in those registers, the corresponding split-screens will not be displayed.

The following is examples of screen split:

When the same value are programmed into more than one screen start position registers, split-screens corresponding to these registers are not displayed.

#### **Table 2 Screen Split**

| Control 1<br>Register |     |   | ber of<br>tive scr |   |   |  |

|-----------------------|-----|---|--------------------|---|---|--|

| SP1                   | SPO | 1 | 2                  | 3 | 4 |  |

| 0                     | 0   | 0 | -                  | - | - |  |

| 0                     | 1   | 0 | 0                  | - | - |  |

| 1                     | 0   | 0 | 0                  | 0 | - |  |

| 1                     | 1   | 0 | 0                  | 0 | 0 |  |

<sup>:</sup> effective screen

: invalid screen

Figure 6-C Screen Split (Example 3)

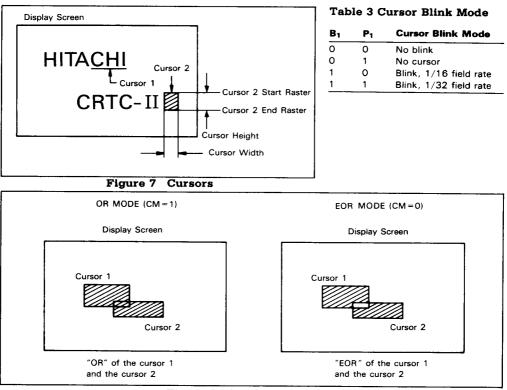

### CURSOR CONTROL

The CRTC-II can display two separate cursors (cursor 1, cursor 2) simultaneously on the screen. These two cursors are controlled independently. The cursor 1 is always valid, while the cursor 2 becomes valid by setting the  $C_2$  bit of the control 3 register (R32).

In the MPRAM mode, the cursor 2 cannot be displayed. The CRTC-II controls cursors as follows:

Starting Position Starting position is controlled by the cursor 1 address registers (R14, R15), and the cursor 2 address registers (R36, R37).

2) Cursor Heights The heights of the cursor 1 and the cursor 2 can be specified independently in units of rasters by the cursor start registers (R10, R34), and the cursor end registers (R11, R35).

3) Cursor Widths

The widths of the cursor 1 and the cursor 2 can be specified independently in units of characters by the cursor width registers (R38, R39). The R38 register is enabled when 1 is set into the CW1 bit of the control 3 register (R32). The R39 register's enable bit is the CW2.

If the cursor width extends over the following row, the cursor in the following row will not be displayed.

- 4) Cursor Blink Cursor display, non-display, and blink rate can be controlled by the bits B<sub>1</sub> and P<sub>1</sub> of the cursor 1 start register (R10), and bits the B<sub>2</sub> and P<sub>2</sub> of the cursor 2 start register (R34).

- 5) Cursor Display Mode

When the cursor 1 and the cursor 2 are overlapped on the screen, cursor display mode in the overlapped area can be selected by the CM bit of the control 3 register (R32), as shown in Figure 8.

### Figure 8 Cursor Display Mode

### O HITACHI

# Figure 9 Raster Scanning Example

CHITACHI

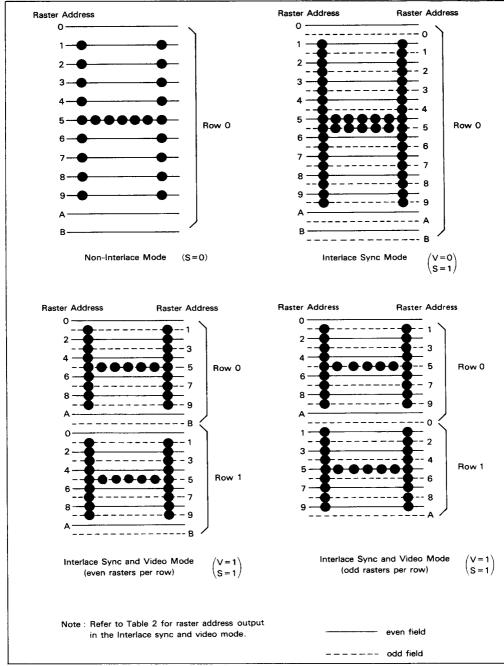

In the Interlace sync mode, the rasters in the odd field are placed downward by 1/2 raster line space from those in the even field because of the difference in HSYNC/VSYNC phases between two alternating fields.

In the Interlace sync and video mode, the placement of the rasters is the same as in the Interlace sync mode. However, the alternating even and odd resters are displayed in the alternating even and odd fields. Note that the raster address is supplied in the different way according to the total number of rasters in a row, even or odd, as shown in Table 4. Figure 9 illustrates the raster scanning example in each mode.

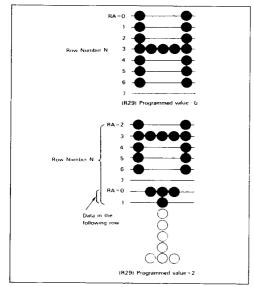

#### SMOOTH SCROLLING

Smooth scrolling in the vertical direction can be accomplished by changing the start raster address in a character row. Whether scrolling in each split-screen is available or not can be selected. Selected split-screens scroll in the same way up to four split-screens simultaneously.

Smooth scrolling is performed by the bits  $SS_1$ - $SS_4$  of the control 2 register (R31), and the smooth scrolling register (R29). It can be used in the Non-Interlace mode and the Interlace sync mode, but not in the Interlace sync and video mode.

# Tabel 4Start Raster Address for Each<br/>Row (In Interlace sync and<br/>video mode)

| No. of Rasters                        | Field                       |                             |  |  |

|---------------------------------------|-----------------------------|-----------------------------|--|--|

| per Row                               | Even Field                  | Odd Field<br>Odd address    |  |  |

| Even                                  | Even address                |                             |  |  |

| Odd Even Char. Row*<br>Odd Char. Row* | Even address<br>Odd address | Odd address<br>Even address |  |  |

\* The start row address is assumed to be 0 (even).

Figure 10 Smooth Scrolling

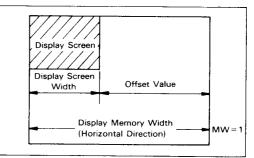

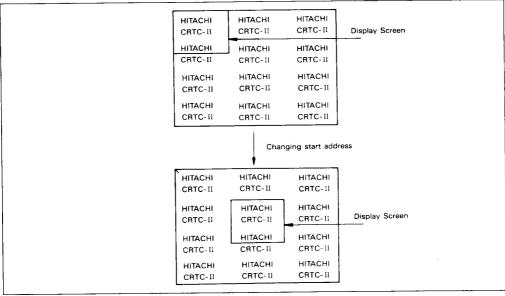

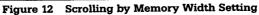

### MEMORY WIDTH SETTING

The offset value is the difference between the display screen width and the display memory width in the horizontal direction. It can be specified in units of characters. (See Figure. 11)

Scrolling in any direction can be accomplished in units of characters, by setting the display memory width (horizontal direction) and the offset value, and by changing the start memory addresses. This is performed by the memory width offset register (R33) and the MW bit of the control 3 register (R32).

Figure 11 Memory Width

## **OHITACHI**

Figure 13 Memory Address and Raster Address in Memory Width Setting

# **OHITACHI**

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300 55

This Material Copyrighted By Its Respective Manufacturer

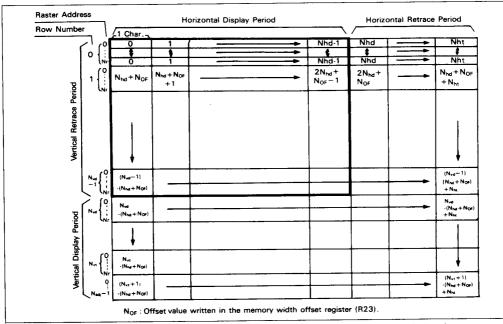

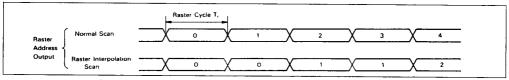

#### **RASTER INTERPOLATION**

Raster interpolation function increments the raster address every two rasters, doubling the vertical scan cycle; thus the display image is doubled in the vertical direction.

Raster interpolation function is controlled by the RI bit of the control 2 register (R31). This function can be used in the non-interlace mode and the interlace sync mode, but not in the interlace sync and video mode. Figure 14 is a display example using raster interpolation function.

Figure 14 Raster Interpolation

Figure 15 Raster Address Output and Raster Interpolation

#### **EXTERNAL SYNCHRONIZATION**

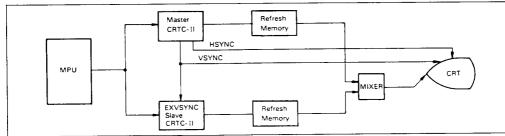

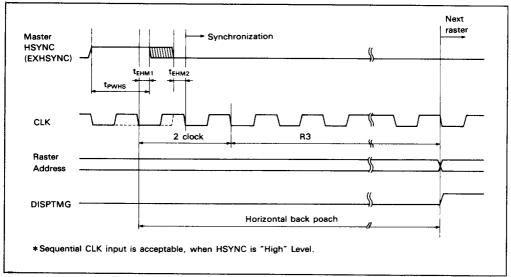

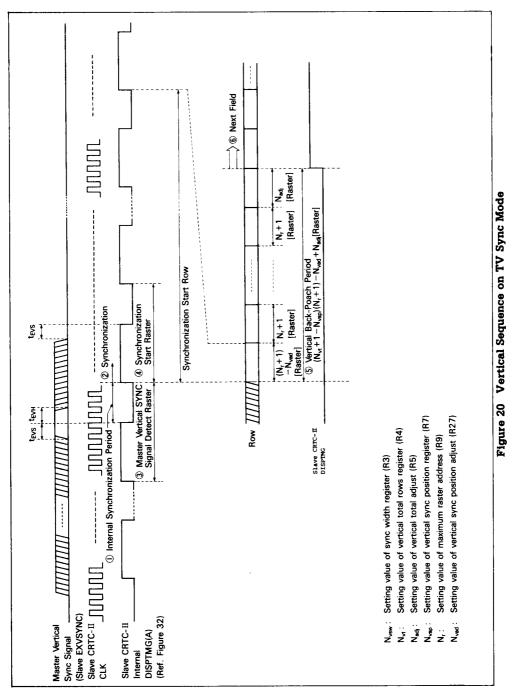

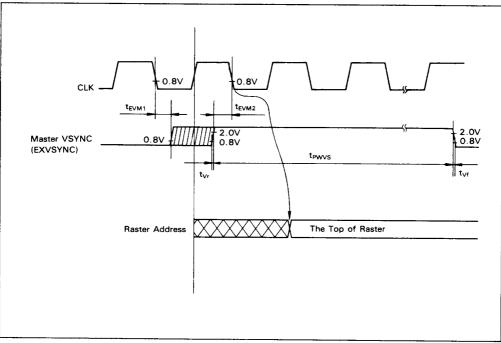

There are master/slave mode and TV sync mode in external synchronization.

The external synchronization is controlled by the bits VE, VS, and TV of the control 1 register (R30).

Master/slave mode is used to synchronize slave CRTC-IIs with a master CRTC-II by the VSYNC of a master CRTC-II. When superimposing a master screen with slave screen on the same CRT, clocks of a master and slave CRTC-IIs can operate in different frequency under conditions as follows.

- Phase of a master CRTC-II clock matches with a slave CRTC-II clock at rising edge of VSYNC.

- (2) Both master and slave CRTC-IIs have the same horizontal/vertical scan cycle.

Figure 16 illustrates the system configuration. In the Interlace sync mode and the Interlace sync and video mode, the control 1 register must be set as to provide a VSYNC output in odd fields of a master CRTC-II.

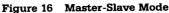

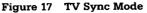

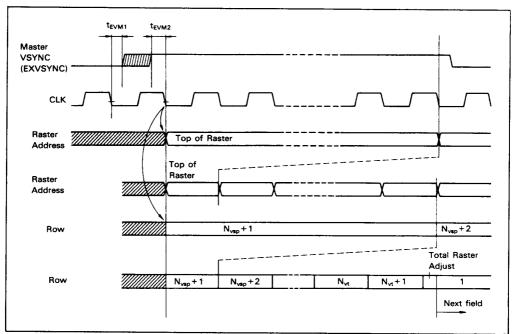

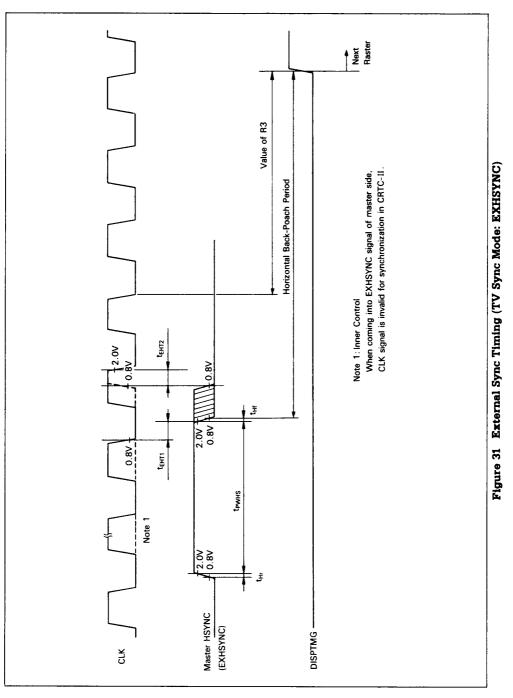

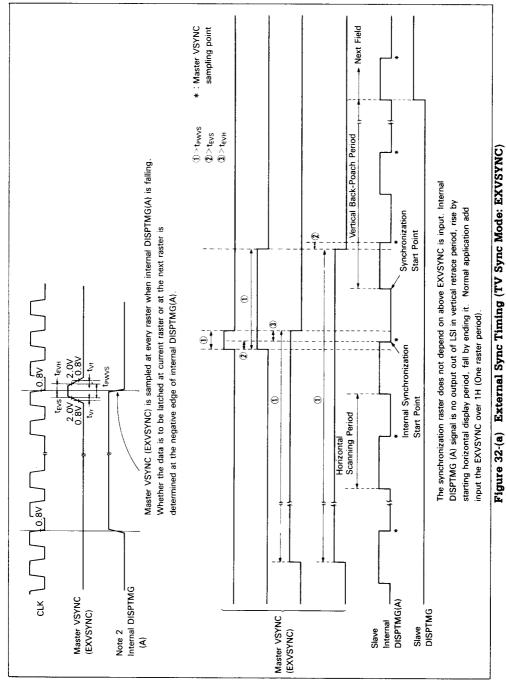

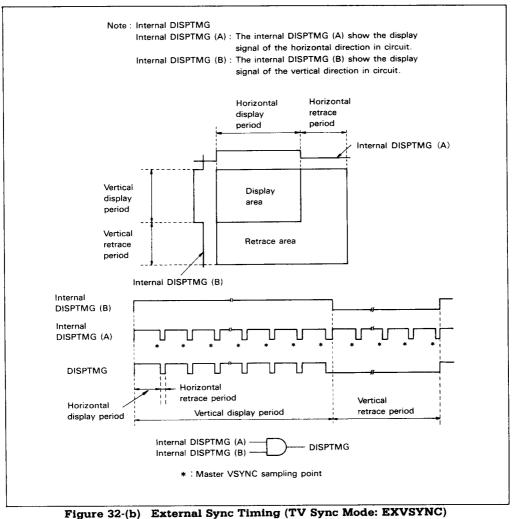

TV sync mode is used to synchronize the CRTC-II with the HSYNC and VSYNC signals of a TV's video signal.

In the TV sync mode, the HSYNC/EXHSYNC pin inputs the EXHSYNC signal and the VSYNC/EXVSYNC pin inputs the EXVSYNC signal. The length of horizontal back porch is specified by the bits 0-3 of the sync width register (R3).

Figure 17 illustrates the system configuration.

In TV sync mode, when performing raster interpolation of slave CRTC-IIs, Interlace sync mode or Interlace sync and video mode must not be set in a master CRTC-II; this causes the screen moves up and down by one raster.

In the Interlace sync and video mode, the TV sync mode cannot be used.

## CHITACHI

### **Table 5 External Synchronization**

|    |    |   |                          |                   |                   | Function |                                                                                                                                                                                  |

|----|----|---|--------------------------|-------------------|-------------------|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VE | vs | т | Mode                     | EXHSYNC<br>/HSYNC | EXVSYNC<br>/VSYNC | DISPTMG  | States                                                                                                                                                                           |

| 0  | 0  | 0 | Master<br>/slave<br>mode | OUTPUT            | OUTPUT            | Active   | Set as master CRTC-II in master-slave mode.<br>"000" is to be set when CRTC-II is in nomal<br>states (HD6845 compatible mode) or master<br>mode.                                 |

| 0  | 1  | 0 | -                        |                   |                   | "Low"    | Set as master CRTC-II in master slave mode.<br>Display is inhibited by setting DISPTMG "0".<br>VSYNC signal is supplied only in odd field scan<br>except the non-interlace mode. |

| 1  | 0  | 0 | -                        | OUTPUT            | INPUT             | Active   | Set as slave CRTC-II in master slave mode.<br>EXHSYNC is not used for the synchronization.                                                                                       |

| 1  | 1  | 0 | _                        |                   |                   | "Low"    | Set as slave CRTC-II in master slave mode.<br>EXVSYNC is used for the synchronization.                                                                                           |

| 0  | 0  | 1 | TV sync<br>mode          | INPUT             | OUTPUT            | Active   | Program inhibited                                                                                                                                                                |

| 0  | 1  | 1 | -                        |                   |                   | "Low"    | Program inhibited                                                                                                                                                                |

| 1  | 0  | 1 | _                        | INPUT             | INPUT             | Active   | Set as slave CRTC-II in TV sync mode.<br>EXHSYNC, EXVSYNC inputs are used as sync<br>signal.                                                                                     |

| 1  | 1  | 1 |                          |                   |                   | "Low"    | Set as slave CRTC-II in TV sync mode. Display<br>is inhibited by setting DISPTMG "0".<br>EXHSYNC, EXVSYNC inputs are used as sync<br>signal.                                     |

Note : Slave CRTC-IIs are always Non-Interlace mode in TV sync mode.

# O HITACHI

Figure 18 Synchronization Sequence

Figure 19 Hosizontal Sequence on TV Sync Mode

CHITACHI

# **OHITACHI**

Hitachi America, Ltd. • Hitachi Plaza • 2000 Sierra Point Pkwy. • Brisbane, CA 94005-1819 • (415) 589-8300

HD6345/HD6445

2

59

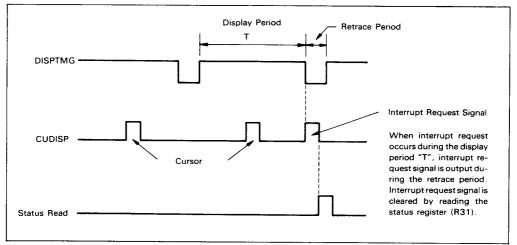

#### INTERRUPT REQUEST

An interrupt request signal to the MPU is output in the timing shown in Figure 21. Interrupt request is generated by the vertical retrace period, or the light pen input.

Reading the status register (R31) clears interrupt request signal. Thus, if the MPU does not read the status register (R31) when an interrupt request is generated, an interrupt request signal is output during all the horizontal and vertical retrace periods.

In the MPRAM mode, an interrupt request signal is not output.

An interrupt request is controlled by the bits IB and IL of the control 1 register (R30).

#### Table 6 Interrupt Control

| IB | IL | Source of Interrupt Reque | st |

|----|----|---------------------------|----|

|    |    |                           |    |

| 0 | 0 | None                                   |

|---|---|----------------------------------------|

| 0 | 1 | Light pen strobe                       |

| 1 | 0 | Vertical retrace                       |

| 1 | 1 | links and states and (an oration) of a |

1 1 Light pen strobe and/or vertical retrace

Figure 21 Interrupt Timing

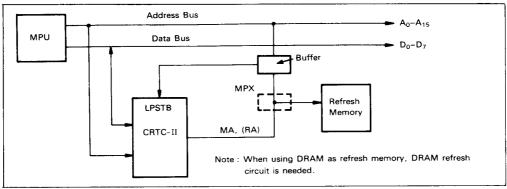

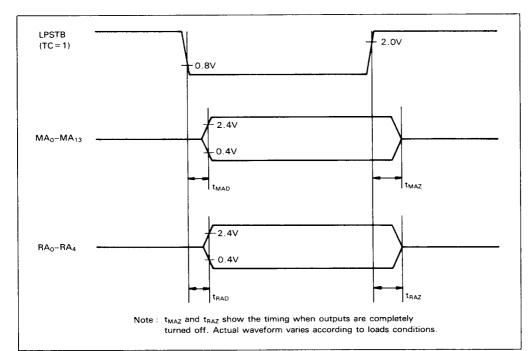

### THREE-STATE CONTROL OF MA/RA

Memory address (MA) and raster address (RA) outputs can be three-stated, using the TSC input pin. Three-state control is enabled by setting the TC bit of the control 3 register (R32).

When three-state control is used, a multiplexer (MPX) to select address lines from the MPU and the CRTC-II for refresh memory is not required, as shown in Figure 22.

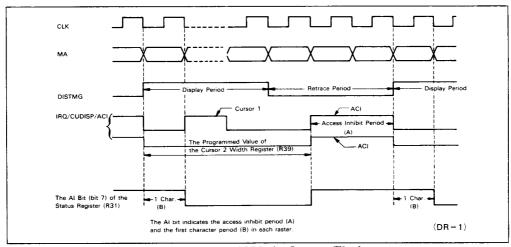

#### MPRAM MODE

When the MPRAM mode is selected (DR=1), the HD6445 generates a programmable timing signal from the access inhibit pin. This signal, shown in Figure 23 as access inhibit period, provides the timing for the MPU to access to multi-port memory.

In the MPRAM mode, an interrupt request signal is not output, and the cursor 2 is not displayed.

This timing signal is controlled by the DR bit of the control 3 register (R32), and the cursor 2 width register (R39).

Figure 22 Three-State Control

####

#### SKEW

| $D_1$ | Do | DISPTMG                      |

|-------|----|------------------------------|

| 0     | 0  | No skew                      |

| 0     | 1  | One character skew           |

| 1     | 0  | Two character skew           |

| 1     | 1  | Not available ("Low" fixing) |

### C1 C0 CUDISP

| 0 | 0 | No skew                      |

|---|---|------------------------------|

| 0 | 1 | One character skew           |

| 1 | 0 | Two character skew           |

| 1 | 1 | Not available ("Low" fixing) |

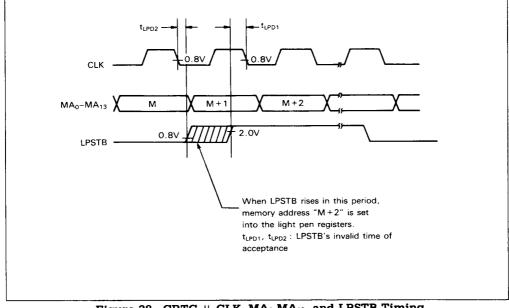

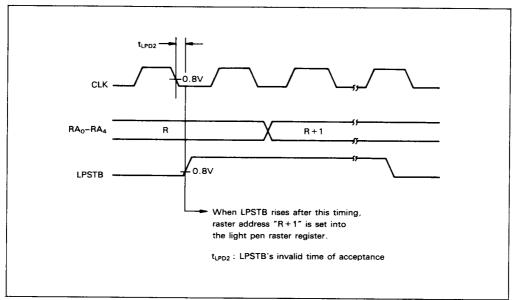

#### LIGHT PEN

The R16 and R17 registers latches the light pen detection address. R28 register latches the light pen detection raster address and the detection period. The DP bit is set to 1 when the LPSTB is detected during the display period; cleared 0 during the retrace period.

#### VERTICAL SYNC POSITION ADJUST

The R27 register performs a fine adjustment to the vertical sync signal output in units of rasters. The VSYNC signal is supplied after the delay of Nvad rasters. R27 register is enabled when 1 is set into the SY bit of the control 1 register (R30).

#### STATUS

| E  | Status                        |

|----|-------------------------------|

| 0  | During odd field display      |

| 1  | During even field display     |

| SB | Status                        |

| 0  | Not during vertical retrace   |

| 1  | During vertical retrace       |

| SL | Status                        |

| 0  | Light pen strobe not detected |

| 1  | Light pen strobe detected     |

| AI | Status                        |

| 0  | Refresh memory access allowed |

Refresh memory access inhibited

### **INTERNAL REGISTER ASSIGNMENT**

|           |    | Register<br>Address                         | _    |                                    | _                 |                  |      | D               | . B             | ••       |     |     |                 |     |      |

|-----------|----|---------------------------------------------|------|------------------------------------|-------------------|------------------|------|-----------------|-----------------|----------|-----|-----|-----------------|-----|------|

|           |    |                                             | Reg. |                                    | Program           |                  |      |                 | ta B            |          |     | -   |                 | _   |      |

| <u>Cs</u> | KŞ | 543210                                      | No.  | Register Name                      | Unit              | Symbo            | IR/W | 7               | 6               | 5        | 4   | 3   | 2               | 1   | 0    |

| 1         | ×  | ××××××                                      | -    | -                                  | -                 | -                | -    |                 |                 |          |     |     |                 |     | //// |

| 0         | 0  | $\times \times \times \times \times \times$ | AR   | ADDRESS REGISTER                   | -                 | -                | w    |                 |                 | <u>,</u> |     |     |                 |     |      |

| ō         | 1  | 000000                                      | RO   | HORIZONTAL TORAL CHARACTERS        | character         | Nht              | w    |                 |                 |          |     |     |                 |     |      |

| ō         | 1  | 000001                                      | R1   | HORIZONTAL DISPLAYED<br>CHARACTERS | character         | Nhd              | w    |                 |                 |          |     |     |                 |     |      |

| 0         | 1  | 000010                                      | R2   | HORIZONTAL SYNC POSITION           | character         | Nhsp             | w    |                 |                 |          |     |     |                 |     |      |

| 0         | 1  | 000011                                      | R3   | SYNC WIDTH                         | *                 | Nvsw,<br>Nhsw    | w    | Wv3             | Wv <sub>2</sub> | Wv       | Wvo | Whg | Wh <sub>2</sub> | Whη | Who  |

| 0         | 1  | 000100                                      | R4   | VERTICAL TORAL ROWS                | row               | Nvt              | w    |                 |                 |          |     |     |                 |     |      |

| 0         | 1  | 000101                                      | R5   | VERTICAL TORAL ADJUST              | raster            | Nadj             | w    | $\overline{//}$ | ///             | ///      | 1.  |     |                 |     |      |

| 0         | 1  | 000110                                      | R6   | VERTICAL DISPLAYED ROWS            | row               | Nvd              | W    |                 |                 |          |     |     |                 |     |      |

| 0         | 1  | 000111                                      | R7   | VERTICAL SYNC POSITION             | row               | N∨sp             | w    |                 |                 |          |     |     |                 |     |      |

| 0         | 1  | 001000                                      | R8   | INTERLACE MODE AND SKEW            |                   | -                | W    | C1              | Co              | D1       | Do  | /// | ///             | V   | S    |

| 0         | 1  | 001001                                      | R9   | MAX RASTER ADDRESS                 | raster            | Nr               | w    | 11              | ////            | 1///     | 1   |     |                 |     |      |

| 0         | 1  | 001010                                      | R10  | CURSOR 1 START                     | raster            | Ncs <sub>1</sub> | w    | $\overline{/}$  | Β,              | P1       |     |     |                 |     |      |

| 0         | 1  | 001011                                      | R11  | CURSOR 1 END                       | raster            | Nce <sub>1</sub> | w    |                 |                 |          | 1   |     |                 |     |      |

| 0         | 1  | 001100                                      | R12  | SCREEN 1 START ADDRESS (H)         | memory<br>address | -                | R/Ŵ  |                 |                 |          | *   |     |                 |     |      |

1

Note 1) \*: Vertical: raster/Horizontal: character.

2) 2 : "0" is to be set, since these bits may be used in the future.

#### CHITACHI

2

|    |    | Register<br>Address | Reg. |                               | Program           |                  |     | Dat           | a Bi             | it               |      |      |    |    |       |

|----|----|---------------------|------|-------------------------------|-------------------|------------------|-----|---------------|------------------|------------------|------|------|----|----|-------|

| CS | RS | 543210              | No.  | Register Name                 | Unit              | Symbol           | R/W | 7             | 6                | 5                | 4    | 3    | 2  | 1  | 0     |

| 0  | 1  | 001101              | R13  | SCREEN 1 START ADDRESS (L)    | memory<br>address | -                | R/W |               |                  | <u> </u>         |      |      |    |    |       |

| ō  | 1  | 001110              | R14  | CURSOR 1 ADDRESS (H)          | memory<br>address | -                | R/W |               |                  |                  |      |      |    |    |       |

| 0  | 1  | 001111              | R15  | CURSOR 1 ADDRESS (L)          | memory<br>address | -                | R/W |               |                  |                  |      |      |    |    |       |

| 0  | 1  | 010000              | R16  | LIGHT PEN (H)                 | -                 | -                | R   |               |                  | 1                |      |      |    |    |       |

| 0  | 1  | 010001              | R17  | LIGHT PEN (L)                 | -                 |                  | R   |               |                  |                  |      |      |    |    |       |

| 0  | 1  | 010010              | R18  | SCREEN 2 START POSITION       | row               | -                | R/W |               |                  | ,                |      |      |    |    |       |

| 0  | 1  | 010011              | R19  | SCREEN 2 START ADDRESS (H)    | memory<br>address | -                | R/W |               |                  | /                |      |      |    |    |       |

| 0  | 1  | 010100              | R20  | SCREEN 2 START ADDRESS (L)    | memoey<br>address | -                | R/W | '             |                  |                  |      |      |    |    |       |

| 0  | 1  | 010101              | R21  | SCREEN 3 START POSTION        | row               | -                | R/W | <u>'</u>      |                  |                  |      |      |    |    |       |

| 0  | 1  | 010110              | R22  | SCREEN 3 START ADDRESS (H)    | memory<br>address | -                | R/W |               |                  |                  |      |      |    |    |       |

| 0  | 1  | 010111              | R23  | SCREEN 3 START ADDRESS (L)    | memory<br>address | _                | R/W | /             |                  |                  |      |      |    |    |       |

| 0  | 1  | 011000              | R24  | SCREEN 4 START POSITION       | row               |                  | R/W |               |                  | <del>, , .</del> |      |      |    |    |       |

| 0  | 1  | 011001              | R25  | SCREEN 4 START ADDRESS (H)    | memory<br>address | -                | R/M | `//           |                  |                  |      |      |    |    |       |

| 0  | 1  | 011010              | R26  | SCREEN 4 START ADDRESS (L)    | memory<br>address | -                | R/M | /             |                  |                  |      |      |    |    |       |

| 0  | 1  | 011011              | R27  | VERTICAL SYNC POSITION ADJUST | raster            | Nvad             | w   |               | ///              |                  | 4_   |      |    |    |       |

| 0  | 1  | 011100              | R28  | LIGHT PEN RASTER              | -                 | -                | R   | DP            | ]]]              | ///              | 4    |      |    |    |       |

| ō  | 1  | 011101              | R29  | SMOOTH SCROLLING              | raster            | Nss              | R/M | \$ <i>'//</i> |                  |                  | 1    |      |    |    |       |

| 0  | 1  | 011110              | R30  | CONTROL 1                     | -                 | -                | w   | VE            | VS               | IB               | IL   | SY   | TV | SP | 1 SPO |

| 0  | 1  | 011111              | R31  | CONTROL 2                     | -                 | -                | w   | SS            | ss i             | 3 SS             | 2 SS | I RI |    |    | ///// |

|    |    |                     |      | STATUS                        | -                 | -                | R   | Ał            |                  | $\square$        |      |      | É. | SB | SL    |

| 0  | 1  | 100000              | R32  | CONTROL 3                     | -                 | -                | W   |               | C2               | C/               | V1CV | /2MW | тс | DR |       |

| 0  | 1  | 100001              | R33  | MEMORY WIDTH OFFSET           | character         | Nof              | R/W |               | ,                |                  |      |      |    |    |       |

| 0  | 1  | 100010              | R34  | CURSOR 2 START                | raster            | Ncs <sub>2</sub> | w   |               | ∑ <sup>B</sup> 2 | P2               |      |      |    |    |       |

| 0  | 1  | 100011              | R35  | CURSOR 2 END                  | raster            | Nce <sub>2</sub> | w   |               |                  |                  |      |      |    |    |       |

| 0  | 1  | 100100              | R36  | CURSOR 2 ADDRESS (H)          | memory<br>address | -                | R/W |               |                  |                  |      |      |    |    |       |

| 0  | 1  | 100101              | R37  | CURSOR 2 ADDRESS (L)          | memory<br>address | -                | R/W | 1             |                  |                  |      |      |    |    |       |

| 0  | 1  | 100110              | R38  | CURSOR 1 WIDTH                | character         | Ncw1             | R/W | /             |                  |                  |      |      |    |    |       |

| 0  | 1  | 100111              | R39  | CURSOR 2 WIDTH                | character         | Ncw <sub>2</sub> | R/W | /             |                  |                  |      | •    |    |    |       |

Note

#### RESET

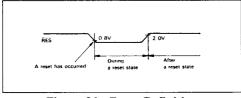

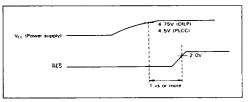

The  $\overline{\text{RES}}$  functions as a reset input signal only while the LPSTB is "L". "Reset" is definable in two stages.

(1) "During a reset state" indicates the period that the RES remains "L".

Figure 24 Reset Definition

(2) "After a reset state" indicates the state after the RES transition from "L" to "H".

The pin status during a reset state is in Table 7.

Figure 25 Reset at Power-on

| Pin No. |                |                                                          |                             | Input/           |                                                                                |  |  |  |

|---------|----------------|----------------------------------------------------------|-----------------------------|------------------|--------------------------------------------------------------------------------|--|--|--|

| DP-40   | CP-44          | Symbol                                                   | Pin Name                    | Output           | Pin Status                                                                     |  |  |  |

| 1       | 1, 2           | V <sub>SS</sub> (V <sub>SS</sub> 1, V <sub>SS</sub> 2)** | V <sub>SS</sub>             | -                | -                                                                              |  |  |  |

| 2       | 3              | RES                                                      | RESET                       | Input            | _                                                                              |  |  |  |

| 3       | 4              | LPSTB                                                    | LIGHT PEN STROBE            | Input            | "L" level signal requested to                                                  |  |  |  |

|         |                | TSC                                                      | THREE STATE CONTROL         | Input            | be supplied                                                                    |  |  |  |

| 4-17    | 5-11<br>13-19  | MAO-MA13                                                 | MEMORY ADDRESS 0-13         | Output           | Goes "L" immediately after reset                                               |  |  |  |

| 18      | 20             | DISPTMG                                                  | DISPLAY TIMING              | Output           | Goes "L" immediately after<br>reset                                            |  |  |  |

| 19      | 21             | CUDISP                                                   | CURSOR DISPLAY              | Output           | Goes "L" immediately after                                                     |  |  |  |

|         |                | ACI                                                      | ACCESS INHIBIT              | Output           | reset                                                                          |  |  |  |

|         |                | IRQ                                                      | INTERRUPT REQUEST           | Output           | -                                                                              |  |  |  |

| 20      | 22, 23         | Vcc (Vcc1, Vcc2)**                                       | Vcc                         | _                | _                                                                              |  |  |  |

| 21      | 24             | CLK                                                      | CHARACTER CLOCK             | Input            | Not affected                                                                   |  |  |  |

| 22      | 25             | R/W (WR)*                                                | READ/WRITE (WRITE)*         | Input            | Not affected                                                                   |  |  |  |

| 23      | 26             | E (RD)*                                                  | ENABLE (READ)*              | Input            | Not affected                                                                   |  |  |  |

| 24      | 27             | RS                                                       | REGISTER SELECT             | Input            | Not affected                                                                   |  |  |  |

| 25      | 28             | <u>cs</u>                                                | CHIP SELECT                 | Input            | Not affected                                                                   |  |  |  |

| 33-26   | 37-35<br>33-29 | D0-D7                                                    | DATA BUS 0-7                | Input/<br>Output | Not affected                                                                   |  |  |  |

| 38-34   | 42-38          | RAO-RA4                                                  | RASTER ADDRESS 0-4          | Output           | Goes "L" immediately after reset                                               |  |  |  |

| 39      | 43             | HSYNC                                                    | HORIZONTAL SYNC             | Output           | Outputs HSYNC signal until                                                     |  |  |  |

|         |                | EXHSYNC                                                  | EXTERNAL HORIZONTAL<br>SYNC | Input            | external sunch mode is set<br>into the control 1 register<br>(R29) after reset |  |  |  |

| 40      | 44             | VSYNC                                                    | VERTICAL SYNC               | Output           | Outputs VSYNC signal until                                                     |  |  |  |

|         |                | EXVSYNC                                                  | EXTERNAL VERTICAL<br>SYNC   | Input            | external sync mode is set int<br>the control 1 register (R25<br>after reset    |  |  |  |

#### Table 7 Pin Status during a Reset State

Note : \* marked pins are of the HD6445

\* \* marked pins are of the CP-44

### CHITACHI

# **ABSOLUTE MAXIMUM RATINGS**

| Item                           |          | Symbol               | Rating                       | Unit |

|--------------------------------|----------|----------------------|------------------------------|------|

| Supply Voltage                 |          | Vcc*                 | -0.3 to +7.0                 | v    |

| Input Voltage                  |          | V <sub>in</sub> *    | -0.3 to V <sub>CC</sub> +0.3 | V    |

| Operating Temperature          |          | T <sub>opr</sub>     | -20 to +75                   | .C   |

| Storage Temperature            |          | T <sub>stg</sub>     | -55 to +150                  | ۰C   |

| Allowable Output Current       | Data Bus | lo **                | 5                            | mA   |

|                                | Others   | -                    | 3                            | mA   |

| Total Allowable Output Current |          | Σl <sub>0</sub>  *** | 60                           | mA   |

- \* This value is in reference to V<sub>SS</sub>=0V.

- \*\* The allowable output current is the maximum current that may be drawn from, of flow out to, one output pin or one input/output common pin.

- \* \*\* The total allowable output current is the toral sum of currents that may be drawn from, or flow out to, output pins or input/output common pin.

- Note: Using an LSI beyond its maximum ratings may result in its permanent destruction. LSI's should usually be under recommended operating conditions.

Exceeding any of these conditions may adversely affect its reliability.

# **RECOMMENDED OPERATING CONDITIONS**

| item                     |       | Symbol           | Min  | Тур | Max  | Unit |

|--------------------------|-------|------------------|------|-----|------|------|

| Power Supply Voltage     | DP-40 | Vcc*             | 4.75 | 5.0 | 5.25 | v    |

|                          | CP-44 |                  | 4.5  |     | 5.5  |      |

| Input Low Level Voltage  |       | VIL*             | -0.3 |     | 0.8  | V    |

| Input High Level Voltage |       | VIH*             | 2.0  | _   | Vcc  | V    |

| Operating Temperature    |       | T <sub>opr</sub> | -20  | 25  | 75   | °C   |

\* This value is in reference to  $V_{SS} = 0V$ .

### **ELECTRICAL CHARACTERISTICS**

#### DC CHARACTERISTICS

$(V_{cc}=5.0V \pm 5\% \text{ (DLP)}, 5.0 \pm 10\% \text{ (PLCC)}, V_{ss}=0V, T_s=-20 \text{ to } +75^{\circ}C \text{ (Normal)} -40 \text{ to } +85^{\circ}C \text{ (J), unless otherwise noted)}$

| Item<br>Input High Level Voltage                                  |                                                                    | Symbol           | Min             | Typ* | Max  | Unit | <b>Test Conditions</b>                                                                                               |                        |

|-------------------------------------------------------------------|--------------------------------------------------------------------|------------------|-----------------|------|------|------|----------------------------------------------------------------------------------------------------------------------|------------------------|

|                                                                   |                                                                    | VIH              | 2.0             | _    | Vcc  | V    |                                                                                                                      |                        |

| Input Low Level V                                                 | oltage                                                             | VIL              | -0.3            | -    | 0.8  | V    |                                                                                                                      |                        |

| Input Leak Input except<br>Current D <sub>0</sub> -D <sub>7</sub> |                                                                    | l <sub>in</sub>  | l <sub>in</sub> | -2.5 |      | 2.5  | μA                                                                                                                   | $V_{in}$ = 0 to 5.25 V |

| Three-State<br>(Off State)<br>Input Current                       | D <sub>0</sub> -D <sub>7</sub><br>Memory Address<br>Raster Address | I <sub>TSI</sub> | -10             |      | 10   | μA   | $V_{in} = 0.4 \text{ to } 2.4 \text{ V}$<br>$V_{CC} = 5.25 \text{ V}$                                                |                        |

| Output High                                                       | D <sub>0</sub> -D <sub>7</sub>                                     | Voн              | 2.4             | _    | _    | V    | I <sub>OH</sub> =-205µА                                                                                              |                        |

| Level Voltage                                                     | Others                                                             | -                |                 |      |      |      | I <sub>OH</sub> =-100µA                                                                                              |                        |

| Output Low Level                                                  | Voltage                                                            | Vol              |                 |      | 0.4  | V    | I <sub>0L</sub> =1.6mA                                                                                               |                        |

| Input Capacity                                                    | D <sub>0</sub> -D <sub>7</sub><br>EXVSYNC<br>EXHSYNC               | Cin              | _               |      | 12.5 | pF   | $V_{in} = 0 V$<br>$T_a = 25^{\circ}C$<br>f = 1.0 MHz                                                                 |                        |

|                                                                   | Others                                                             |                  | _               | _    | 10   | pF   |                                                                                                                      |                        |

| Output Capacity                                                   |                                                                    | Cout             | _               | _    | 10   | pF   | $V_{in} = 0 V$<br>$T_a = 25^{\circ}C$<br>f = 1.0 MHz                                                                 |                        |

| Power Dissipation                                                 | No Load                                                            | PD               |                 | 50   | 100  | mW   | f <sub>CLK</sub> =4.5 MHz                                                                                            |                        |

|                                                                   | Test Load                                                          | _                |                 | 100  | 200  |      | f <sub>E</sub> =2.0 MHz<br>V <sub>CC</sub> =max<br>V <sub>IH</sub> =V <sub>CC</sub> -1.0 V<br>V <sub>IL</sub> =0.8 V |                        |

\*  $T_a = 2.5^{\circ}C$ ,  $V_{CC} = 5.0 V$

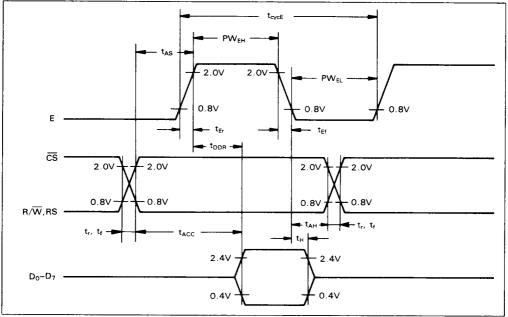

# AC CHARACTERISTICS ( $V_{CC}$ =5.0V ±5 % (DILP), 5V ±10 % (PLCC), $V_{SS}$ =0V, $T_a$ =-20 to +75°C (Normal), -40 to +85°C (J), unless otherwise noted.)

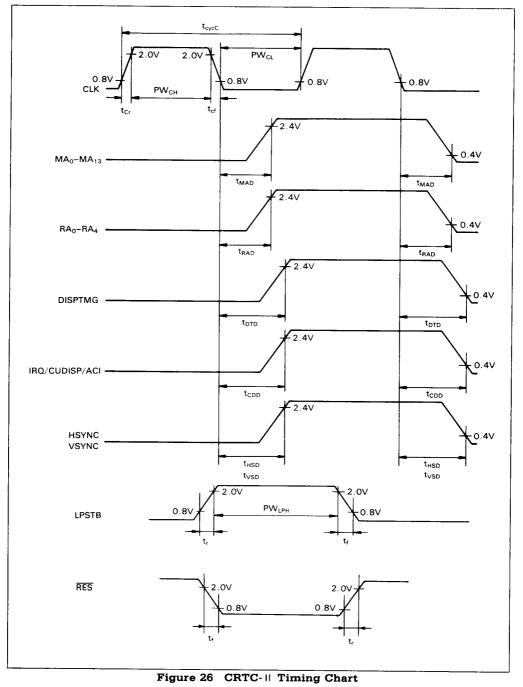

#### 1. Timing of CRT control signal

| ltem                                | Symbol            | Min | Тур | Max | Unit | Reference<br>Figure |

|-------------------------------------|-------------------|-----|-----|-----|------|---------------------|

| Clock Cycle Time                    | tcycC             | 220 | -   | -   | ns   | Fig. 26             |

| Clock High Pulse Width              | РWcн              | 100 | _   | -   | ns   |                     |

| Clock Low Pulse Width               | PWCL              | 100 | _   | -   | ns   |                     |

| Rise and Fall Time for Clock Input  | tcr, tcf          | _   | _   | 20  | ns   |                     |

| Memory Address Delay Time           | t <sub>MAD</sub>  | -   | -   | 80  | ns   |                     |

| Raster Address Delay Time           | t <sub>RAD</sub>  | -   | _   | 80  | ns   |                     |

| DISPTMG Delay Time                  | toto              | _   | -   | 120 | ns   |                     |

| CUDISP Delay Time                   | t <sub>CDD</sub>  | -   | _   | 120 | ns   |                     |

| Horizontal Sync Delay Time          | t <sub>HSD</sub>  | -   | -   | 100 | ns   |                     |

| Vertical Sync Delay Time            | t <sub>VSD</sub>  | 15* |     | 120 | лs   |                     |

| Light Pen Strobe Pulse Width        | PWLPH             | 60  | _   | _   | ns   |                     |

| Light Pen Strobe Uncertain Time of  | t <sub>LPD1</sub> | _   | _   | 70  | ns   | Fig. 28             |

| Acceptance                          | tLPD2             | _   | -   | 0   | ns   | Fig. 29             |

| Memory Address Three-State Off Time | tmaz              | -   | _   | 50  | ns   | Fig. 27             |

| Raster Address Three-State Off Time | tRAZ              | _   | -   | 50  | ns   |                     |

Note\*: Application after mark 7C1

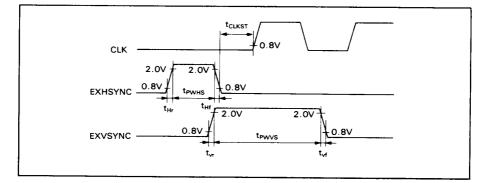

#### 2. External sync timing

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                  | erence<br>Ire |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| $\frac{t_{vf}}{t_{vf}} = -\frac{20}{ns}$ Master Slave Mode. EXVSYNC<br>Uncertain Time of Acceptance<br>External Horizontal Sync Pulse Width<br>$\frac{t_{EVM1}}{t_{EVM2}} = \frac{10}{ns}$ Fig.3<br>$\frac{t_{EVM1}}{t_{EVM2}} = \frac{10}{ns}$ Fig.3    |               |

| Master Slave Mode.     EXVSYNC     tevm1     10     -     -     ns     Fig.3       Uncertain Time of Acceptance     tevm2     60     -     -     ns       External Horizontal Sync Pulse Width     tevms     2+t <sub>cyc</sub> C     -     ns     Fig.3 |               |

| Uncertain Time of Acceptance     tevmin     to     -     ris     ris       External Horizontal Sync Pulse Width     tevms     2 • t <sub>cyc</sub> C     -     ns     Fig.3                                                                              |               |

| tevm2         60         -         ns           External Horizontal Sync Pulse Width         tevms         2 • tevec         -         ns         Fig.3                                                                                                  | 30            |

|                                                                                                                                                                                                                                                          |               |

|                                                                                                                                                                                                                                                          | 31            |

| External Horizontal Sync Rise and Fall Time t <sub>Hr</sub> – – 20 ns                                                                                                                                                                                    |               |

|                                                                                                                                                                                                                                                          | 32            |

| TV sync mode. EXHSYNC tEHT1 30 ns                                                                                                                                                                                                                        |               |

| Uncertain Time of Acceptance t <sub>EHT2</sub> 50 ns                                                                                                                                                                                                     |               |

| TV Sync mode. EXVSYNC set-up Time t <sub>EVS</sub> 50 ns                                                                                                                                                                                                 |               |

| TV Sync mode. EXVSYNC Hold Time t <sub>EVH</sub> 50 ns                                                                                                                                                                                                   |               |

Note \* : Normal application add input over 1H (One raster period) The above specification is applied after mark 7C1. The following specification is applied before it. The above specification is upward-compatible with the following specification.

### External sync timing

| Symbol          | Min                                           | Тур                                                                                                                                                  | Max                                                                                                                                                                                                                                                                                                                                                    | Unit                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

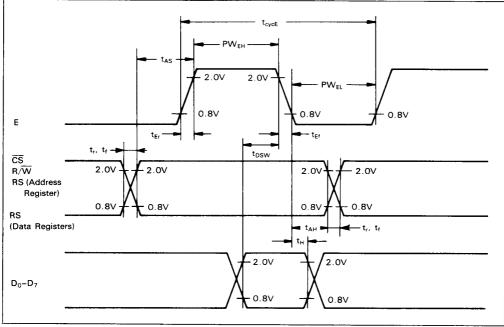

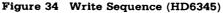

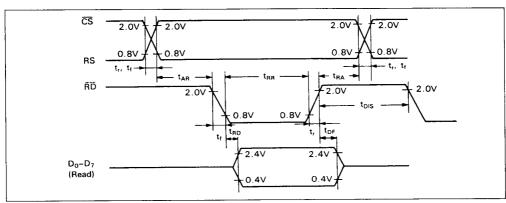

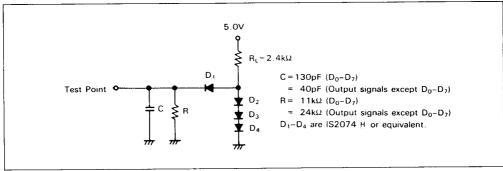

| tCLKST          | 100                                           | _                                                                                                                                                    | _                                                                                                                                                                                                                                                                                                                                                      | ns                                                                                                                                                                                                                                                                                                                                                                                                                                             |