Document Number: MPR121 Rev. 4, 02/2013

√RoHS

# Proximity Capacitive Touch Sensor Controller

The MPR121 is the second generation sensor controller following the initial release of the MPR03x series of devices. The MPR121 features an increased internal intelligence plus Freescale's second generation capacitance detection engine. Some major enhancements include an increased electrode count, a hardware configurable I<sup>2</sup>C address, an expanded filtering system with debounce, and completely independent electrodes with built-in autoconfiguration. The device also features a 13<sup>th</sup> simulated electrode which represents the simultaneous charging of all the electrodes connected together. When used with a touch panel or touch screen array, the 13<sup>th</sup> simulated electrode allows a greater near proximity detection distance and an increased sensing area.

### Features

- 1.71V to 3.6V operation

- 29 μA typical run current at 16 ms sampling interval

- 3 µA in scan stop mode current

- 12 electrodes/capacitance sensing inputs in which 8 are multifunctional for LED driving and GPIO

- Integrated independent autocalibration for each electrode input

- Autoconfiguration of charge current and charge time for each

electrode input

- Separate touch and release trip thresholds for each electrode, providing hysteresis and electrode independence

- I<sup>2</sup>C interface, with IRQ Interrupt output to advise electrode status changes

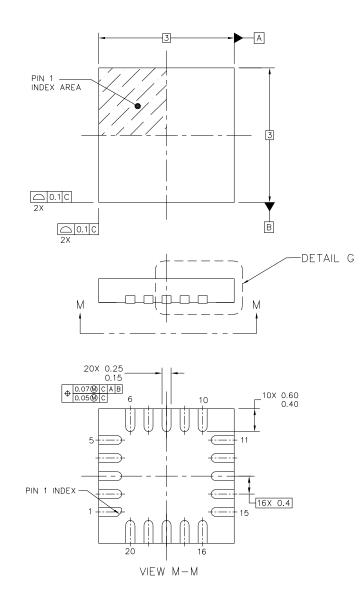

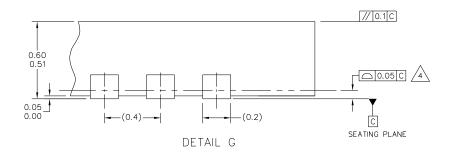

- 3 mm x 3 mm x 0.65 mm 20 lead QFN package

- -40°C to +85°C operating temperature range

#### Implementations

- General Purpose Capacitance Detection

- Switch Replacements

- Touch Pads, Touch Wheel, Touch Slide Bar, Touch Screen Panel

- Capacitance Near Proximity Detection

### **Typical Applications**

- PC Peripherals

- MP3 Players

- Remote Controls

- Mobile Phones

- Lighting Controls

| ORDERING INFORMATION |                                                                                        |                   |         |             |             |  |  |  |

|----------------------|----------------------------------------------------------------------------------------|-------------------|---------|-------------|-------------|--|--|--|

| Device Name          | Device Name Temperature Range Case Number Touch Pads I <sup>2</sup> C Address Shipping |                   |         |             |             |  |  |  |

| MPR121QR2            | -40°C to +85°C                                                                         | 2059 (20-Pin QFN) | 12-pads | 0x5A - 0x5D | Tape & Reel |  |  |  |

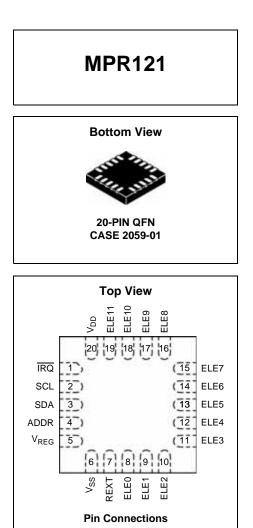

# 1 Pin Descriptions

### Table 1. Pin Descriptions

| Pin No. | Pin Name | Description                                                                                                                                                                           |

|---------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | ĪRQ      | Open Collector Interrupt Output Pin, active low                                                                                                                                       |

| 2       | SCL      | I <sup>2</sup> C Clock                                                                                                                                                                |

| 3       | SDA      | I <sup>2</sup> C Data                                                                                                                                                                 |

| 4       | ADDR     | I <sup>2</sup> C Address Select Input Pin. Connect the ADDR pin to the VSS, VDD, SDA or SCL line, the resulting I <sup>2</sup> C addresses are 0x5A, 0x5B, 0x5C and 0x5D respectively |

| 5       | VREG     | Internal Regulator Node – Connect a 0.1 µF bypass cap to VSS                                                                                                                          |

| 6       | VSS      | Ground                                                                                                                                                                                |

| 7       | REXT     | External Resistor – Connect a 75 k $\Omega$ 1% resistor to VSS to set internal reference current                                                                                      |

| 8       | ELE0     | Electrode 0                                                                                                                                                                           |

| 9       | ELE1     | Electrode 1                                                                                                                                                                           |

| 10      | ELE2     | Electrode 2                                                                                                                                                                           |

| 11      | ELE3     | Electrode 3                                                                                                                                                                           |

| 12      | ELE4     | Electrode 4                                                                                                                                                                           |

| 13      | ELE5     | Electrode 5                                                                                                                                                                           |

| 14      | ELE6     | Electrode 6                                                                                                                                                                           |

| 15      | ELE7     | Electrode 7                                                                                                                                                                           |

| 16      | ELE8     | Electrode 8                                                                                                                                                                           |

| 17      | ELE9     | Electrode 9                                                                                                                                                                           |

| 18      | ELE10    | Electrode 10                                                                                                                                                                          |

| 19      | ELE11    | Electrode 11                                                                                                                                                                          |

| 20      | VDD      | Connect a 0.1 µF bypass cap to VSS                                                                                                                                                    |

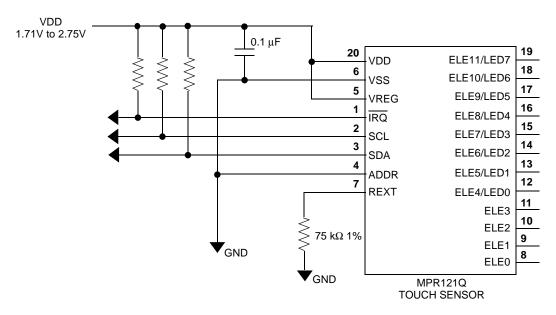

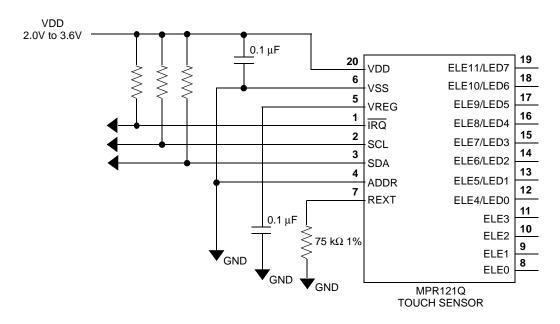

### 2 Schematic Drawings and Implementation

Figure 1. Power Configuration 1: MPR121 runs from a 1.71V to 2.75V supply.

Figure 2. Power Configuration 2: MPR121 runs from a 2.0V to 3.6V supply.

## 3 Device Operation Overview

### **Power Supply**

The VDD pin is the main power supply input to the MPR121 and is always decoupled with a 0.1  $\mu$ F ceramic capacitor to the VSS. Excessive noise on the VDD should be avoided.

The VDD pin has an operational voltage range specification between 1.71V to 3.6V. The internal voltage regulator, which generates current to internal circuitry, operates with an input range from 2.0V to 3.6V. To work with a power supply below 2.0V and to avoid the unnecessary voltage drop, the internal voltage regulator can be bypassed, refer to Figure 1 and Figure 2.

When a power supply is in the range of 1.71V to 2.75V, the VDD and VREG pins can be connected together (Figure 1) so that internal voltage regulator is bypassed. In this configuration, the supply voltage cannot be higher than 2.75V as this is the maximum voltage limit for VREG pin.

When a power supply is higher than 2.75V, it must be connected to the VDD, i.e. configuration as in Figure 2. In this configuration, a separate 0.1  $\mu$ F decoupling ceramic capacitor on VREG to VSS is applied as a bypass cap for internal circuitry. This configuration can work with a VDD supply voltage down to 2.0V. For a typical two dry cell 1.5V batteries application, this configuration covers the entire expected working voltage range from 2.0V to 3.0V.

### **Capacitance Sensing**

The MPR121 uses a constant DC current capacitance sensing scheme. It can measure capacitances ranging from 10 pF to over 2000 pF with a resolution up to 0.01 pF. The device does this by varying the amount of charge current and charge time applied to the sensing inputs.

The 12 electrodes are controlled independently; this allows for a great deal of flexibility in electrode pattern design. An automatic configuration system is integrated as part of the device, this greatly simplifies the individual register setup. Please refer to the Freescale application note, AN3889, for more details.

The voltage measured on the input sensing node is inversely proportional to the capacitance. At the end of each charge circle, this voltage is sampled by an internal 10-bit ADC. The sampled data is then processed through several stages of digital filtering. The digital filtering process allows for good noise immunity in different environments. For more information on the filtering system, refer to application note AN3890.

### **Touch Sensing**

Once the electrode capacitance data is acquired, the electrode touch/release status is determined comparing it to the capacitance baseline value. The capacitance baseline is tracked by MPR121 automatically based on the background capacitance variation.

The baseline value is compared with the current immediate electrode data to determine if a touch or release has occurred. A designer has the ability to set the touch/release thresholds, as well as a touch/release debounce time. This is to eliminate jitter and false touches due to noise. Additional information on baseline capacitance system is covered in application notes AN3891 and AN3892.

#### **Proximity Sensing**

One new feature of the MPR121 is the near proximity sensing system. This means that all of the system's electrodes can be summed together to create a single large electrode. The major advantage of the large electrode is that is can cover a much larger sensing area. The near proximity sensing system can be used while at the same time having separate electrodes by using touch button sensing.

Proximity detection is read as an independent channel and has configuration registers similar to the other 12 channels. When proximity detection is enabled, this "13<sup>th</sup>" measurement channel will be included at the beginning of a normal detection cycle. This system is described in application note AN3893.

#### **LED Driver**

Among the 12 electrode inputs, 8 inputs are designed as multifunctional pins. When these pins are not configured as electrodes, they may be used to drive LEDs or used for general purpose input or output. For more details on this feature, please refer to application note AN3894.

#### **Serial Communication**

The MPR121 is an Inter-Integrated Circuit ( $I^2C$ ) compliant device with an interrupt  $\overline{IRQ}$  pin. This pin is triggered any time a touch or release is detected. The device has a configurable  $I^2C$  address by connecting the ADDR pin to the VSS, VDD, SDA or SCL lines This results in  $I^2C$  addresses of 0x5A, 0x5B, 0x5C and 0x5D. The specific details of this system are described in AN3895. For reference, the register map of the MPR121 is included in Table 2.

#### MPR121

### Table 2. Register Map

| REGISTER                            |        |        |        | Fie      | lds     |         |        |        | Register<br>Address | Initial<br>Value | Auto-<br>Increment<br>Address |

|-------------------------------------|--------|--------|--------|----------|---------|---------|--------|--------|---------------------|------------------|-------------------------------|

| ELE0 - ELE7 Touch Status            | ELE7   | ELE6   | ELE5   | ELE4     | ELE3    | ELE2    | ELE1   | ELE0   | 0x00                | 0x00             |                               |

| ELE8 - ELE11, ELEPROX Touch Status  | OVCF   |        |        | ELEPROX  | ELE11   | ELE10   | ELE9   | ELE8   | 0x01                | 0x00             |                               |

| ELE0-7 OOR Status                   | E7_OOR | E6_OOR | E5_OOR | E4_OOR   | E3_OOR  | E2_OOR  | E1_OOR | E0_OOR | 0x02                | 0x00             |                               |

| ELE8-11, ELEPROX OOR Status         | ACFF   | ARFF   |        | PROX_OOR | E11_OOR | E10_OOR | E9_OOR | E8_OOR | 0x03                | 0x00             |                               |

| ELE0 Electrode Filtered Data LSB    |        |        |        | EFC      | OLB     |         |        |        | 0x04                | 0x00             |                               |

| ELE0 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 0HB    | 0x05                | 0x00             |                               |

| ELE1 Electrode Filtered Data LSB    |        |        |        | EFC      | 01LB    |         |        |        | 0x06                | 0x00             |                               |

| ELE1 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 1HB    | 0x07                | 0x00             |                               |

| ELE2 Electrode Filtered Data LSB    |        |        |        | EFC      | 02LB    |         |        |        | 0x08                | 0x00             |                               |

| ELE2 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 2HB    | 0x09                | 0x00             |                               |

| ELE3 Electrode Filtered Data LSB    |        | •      | •      | EFC      | 03LB    | •       | •      |        | 0x0A                | 0x00             |                               |

| ELE3 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | знв    | 0x0B                | 0x00             |                               |

| ELE4 Electrode Filtered Data LSB    |        | •      | •      | EFC      | 04LB    | •       |        |        | 0x0C                | 0x00             |                               |

| ELE4 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 4HB    | 0x0D                | 0x00             | 1                             |

| ELE5 Electrode Filtered Data LSB    |        |        |        | EFC      | 05LB    |         |        |        | 0x0E                | 0x00             | 1                             |

| ELE5 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 5HB    | 0x0F                | 0x00             | 1                             |

| ELE6 Electrode Filtered Data LSB    |        |        |        | EFC      | D6LB    |         | 1      |        | 0x10                | 0x00             | 1                             |

| ELE6 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 6HB    | 0x11                | 0x00             |                               |

| ELE7 Electrode Filtered Data LSB    |        |        |        | EFC      | D7LB    |         | 1      |        | 0x12                | 0x00             |                               |

| ELE7 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 7HB    | 0x13                | 0x00             | -                             |

| ELE8 Electrode Filtered Data LSB    |        |        |        | EFC      | BLB     |         |        |        | 0x14                | 0x00             | -                             |

| ELE8 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 8HB    | 0x15                | 0x00             |                               |

| ELE9 Electrode Filtered Data LSB    |        |        |        | EFC      | D9LB    |         | l      |        | 0x16                | 0x00             |                               |

| ELE9 Electrode Filtered Data MSB    |        |        |        |          |         |         | EFD    | 9HB    | 0x17                | 0x00             |                               |

| ELE10 Electrode Filtered Data LSB   |        |        |        | EFD      | 10LB    |         |        |        | 0x18                | 0x00             | Register                      |

| ELE10 Electrode Filtered Data MSB   |        |        |        |          |         |         | EFD    | 10HB   | 0x19                | 0x00             | Address + 1                   |

| ELE11 Electrode Filtered Data LSB   |        |        |        | EFD      | 11LB    |         |        |        | 0x1A                | 0x00             | -                             |

| ELE11 Electrode Filtered Data MSB   |        |        |        |          |         |         | EFD    | 11HB   | 0x1B                | 0x00             | -                             |

| ELEPROX Electrode Filtered Data LSB |        |        |        | EEDPI    | ROXLB   |         |        |        | 0x1C                | 0x00             | -                             |

| ELEPROX Electrode Filtered Data MSB |        |        |        |          |         |         | FEDPE  | ROXHB  | 0x1D                | 0x00             | -                             |

| ELEO Baseline Value                 |        |        |        | E        | BV      |         | LIDII  | (OAHD  | 0x1E                | 0x00             |                               |

| ELEO Baseline Value                 |        |        |        |          | BV      |         |        |        | 0x1E                | 0x00             | -                             |

| ELE2 Baseline Value                 |        |        |        |          | BV      |         |        |        | 0x11                | 0x00             |                               |

| ELE2 Baseline Value                 |        |        |        |          | BV      |         |        |        | 0x20                | 0x00             | -                             |

| ELE3 Baseline Value                 |        |        |        |          | BV      |         |        |        | 0x21                | 0x00             | 4                             |

| ELE4 Baseline Value                 |        |        |        |          |         |         |        |        |                     |                  | 4                             |

|                                     |        |        |        |          | BV      |         |        |        | 0x23                | 0x00             | -                             |

| ELE6 Baseline Value                 |        |        |        |          | BV      |         |        |        | 0x24                | 0x00             | -                             |

| ELE7 Baseline Value                 |        |        |        |          | BV      |         |        |        | 0x25                | 0x00             | -                             |

| ELE8 Baseline Value                 |        |        |        |          | BV      |         |        |        | 0x26                | 0x00             | -                             |

| ELE9 Baseline Value                 |        |        |        |          | BV      |         |        |        | 0x27                | 0x00             | -                             |

| ELE10 Baseline Value                |        |        |        |          | )BV     |         |        |        | 0x28                | 0x00             | -                             |

| ELE11 Baseline Value                |        |        |        |          | 1BV     |         |        |        | 0x29                | 0x00             | 4                             |

| ELEPROX Baseline Value              |        |        |        | EPRO     | DXBV    |         |        |        | 0x2A                | 0x00             | 4                             |

| MHD Rising                          |        |        |        |          |         | IDR     |        |        | 0x2B                | 0x00             | -                             |

| NHD Amount Rising                   |        |        |        |          |         | IDR     |        |        | 0x2C                | 0x00             |                               |

| NCL Rising                          |        |        |        |          | LR      |         |        |        | 0x2D                | 0x00             | 4                             |

| FDL Rising                          |        |        | 1      | FD       | lR      |         |        |        | 0x2E                | 0x00             | 4                             |

| MHD Falling                         |        |        |        |          | MF      | IDF     |        |        | 0x2F                | 0x00             |                               |

| NHD Amount Falling                  |        |        |        |          | NF      | IDF     |        |        | 0x30                | 0x00             |                               |

### Table 2. Register Map

| REGISTER                        |          |          | Fie   | lds   |        | Register<br>Address | Initial<br>Value | Auto-<br>Increment<br>Address |

|---------------------------------|----------|----------|-------|-------|--------|---------------------|------------------|-------------------------------|

| NCL Falling                     |          |          | NC    | LF    |        | 0x31                | 0x00             |                               |

| FDL Falling                     |          |          | FC    | DLF   |        | 0x32                | 0x00             |                               |

| NHD Amount Touched              |          |          |       | NHD   | Т      | 0x33                | 0x00             |                               |

| NCL Touched                     |          |          | NC    | LT    |        | 0x34                | 0x00             |                               |

| FDL Touched                     |          |          | FC    | DLT   |        | 0x35                | 0x00             |                               |

| ELEPROX MHD Rising              |          |          |       | MHDPR | OXR    | 0x36                | 0x00             |                               |

| ELEPROX NHD Amount Rising       |          |          |       | NHDPR | OXR    | 0x37                | 0x00             |                               |

| ELEPROX NCL Rising              |          |          | NCLP  | ROXR  |        | 0x38                | 0x00             |                               |

| ELEPROX FDL Rising              |          |          | FDLP  | ROXR  |        | 0x39                | 0x00             |                               |

| ELEPROX MHD Falling             |          |          |       | MHDPR | OXF    | 0x3A                | 0x00             |                               |

| ELEPROX NHD Amount Falling      |          |          |       | NHDPR | OXF    | 0x3B                | 0x00             |                               |

| ELEPROX NCL Falling             |          |          | NCLP  | ROXF  |        | 0x3C                | 0x00             |                               |

| ELEPROX FDL Falling             |          |          | FDLP  | ROXF  |        | 0x3D                | 0x00             |                               |

| ELEPROX NHD Amount Touched      |          |          |       | NHDPR | ОХТ    | 0x3E                | 0x00             |                               |

| ELEPROX NCL Touched             |          |          | NCLP  | ROXT  |        | 0x3F                | 0x00             |                               |

| ELEPROX FDL Touched             |          |          | FDLP  | ROXT  |        | 0x40                | 0x00             |                               |

| ELE0 Touch Threshold            |          |          | E0    | ГТН   |        | 0x41                | 0x00             |                               |

| ELE0 Release Threshold          |          |          | EOF   | RTH   |        | 0x42                | 0x00             |                               |

| ELE1 Touch Threshold            |          |          | E1    | ГТН   |        | 0x43                | 0x00             |                               |

| ELE1 Release Threshold          |          |          | E1F   | RTH   |        | 0x44                | 0x00             |                               |

| ELE2 Touch Threshold            |          |          | E2    | ГТН   |        | 0x45                | 0x00             |                               |

| ELE2 Release Threshold          |          |          | E2F   | RTH   |        | 0x46                | 0x00             |                               |

| ELE3 Touch Threshold            |          | E3TTH    |       |       |        |                     | 0x00             |                               |

| ELE3 Release Threshold          |          | E3RTH    |       |       |        |                     | 0x00             |                               |

| ELE4 Touch Threshold            |          | E4TTH    |       |       |        | 0x49                | 0x00             | Register<br>Address + 1       |

| ELE4 Release Threshold          |          |          | E4F   | RTH   |        | 0x4A                | 0x00             |                               |

| ELE5 Touch Threshold            |          |          | E5    | ГТН   |        | 0x4B                | 0x00             |                               |

| ELE5 Release Threshold          |          |          | E5F   | RTH   |        | 0x4C                | 0x00             |                               |

| ELE6 Touch Threshold            |          |          | E6    | ГТН   |        | 0x4D                | 0x00             |                               |

| ELE6 Release Threshold          |          |          | E6    | RTH   |        | 0x4E                | 0x00             |                               |

| ELE7 Touch Threshold            |          |          | E7    | ГТН   |        | 0x4F                | 0x00             |                               |

| ELE7 Release Threshold          |          |          | E7F   | RTH   |        | 0x50                | 0x00             |                               |

| ELE8 Touch Threshold            |          |          | E8    | ГТН   |        | 0x51                | 0x00             |                               |

| ELE8 Release Threshold          |          |          | E8F   | RTH   |        | 0x52                | 0x00             |                               |

| ELE9 Touch Threshold            |          |          | E9    | ГТН   |        | 0x53                | 0x00             |                               |

| ELE9 Release Threshold          |          |          | E9F   | RTH   |        | 0x54                | 0x00             |                               |

| ELE10 Touch Threshold           |          |          | E10   | ТТН   |        | 0x55                | 0x00             |                               |

| ELE10 Release Threshold         |          |          | E10   | RTH   |        | 0x56                | 0x00             |                               |

| ELE11 Touch Threshold           |          |          | E11   | ттн   |        | 0x57                | 0x00             |                               |

| ELE11 Release Threshold         |          |          | E11   | RTH   |        | 0x58                | 0x00             | 1                             |

| ELEPROX Touch Threshold         | EPROXTTH |          |       |       | 0x59   | 0x00                | 1                |                               |

| ELEPROX Release Threshold       | 1        | EPROXRTH |       |       |        | 0x5A                | 0x00             | 1                             |

| Debounce Touch & Release        | DR       |          |       |       | DT     | 0x5B                | 0x00             | 1                             |

| Filter/Global CDC Configuration | FFI      |          |       | CDC   | ;      | 0x5C                | 0x10             | 1                             |

| Filter/Global CDT Configuration | CDT      |          | S     | FI    | ESI    | 0x5D                | 0x24             | 1                             |

| Electrode Configuration         | CL       | ELEPR    | OX_EN |       | ELE_EN | 0x5E                | 0x00             | 1                             |

| ELE0 Electrode Current          |          |          |       | CDC   | 0      | 0x5F                | 0x00             | 1                             |

| ELE1 Electrode Current          |          |          |       | CDC   | 1      | 0x60                | 0x00             | 1                             |

| ELE2 Electrode Current          |          |          |       | CDC   | 2      | 0x61                | 0x00             | 1                             |

### **MPR121**

### Table 2. Register Map

| REGISTER                          |        |        |                   | Fie   | lds   |         |       |       | Register<br>Address | Initial<br>Value | Auto-<br>Increment<br>Address |

|-----------------------------------|--------|--------|-------------------|-------|-------|---------|-------|-------|---------------------|------------------|-------------------------------|

| ELE3 Electrode Current            |        |        | CDC3              |       |       |         |       |       | 0x62                | 0x00             |                               |

| ELE4 Electrode Current            |        | CDC4   |                   |       |       |         |       |       |                     | 0x00             |                               |

| ELE5 Electrode Current            |        | CDC5   |                   |       |       |         |       |       |                     | 0x00             |                               |

| ELE6 Electrode Current            |        |        |                   |       | CE    | DC6     |       |       | 0x65                | 0x00             |                               |

| ELE7 Electrode Current            |        |        |                   |       | CE    | DC7     |       |       | 0x66                | 0x00             |                               |

| ELE8 Electrode Current            |        |        |                   |       | CE    | DC8     |       |       | 0x67                | 0x00             |                               |

| ELE9 Electrode Current            |        |        |                   |       | CE    | DC9     |       |       | 0x68                | 0x00             |                               |

| ELE10 Electrode Current           |        |        |                   |       | CD    | C10     |       |       | 0x69                | 0x00             |                               |

| ELE11 Electrode Current           |        |        |                   |       | CD    | C11     |       |       | 0x6A                | 0x00             |                               |

| ELEPROX Electrode Current         |        |        |                   |       | CDC   | PROX    |       |       | 0x6B                | 0x00             |                               |

| ELE0, ELE1 Charge Time            |        |        | CDT1              |       |       |         | CDT0  |       | 0x6C                | 0x00             |                               |

| ELE2, ELE3 Charge Time            |        |        | CDT3              |       |       |         | CDT2  |       | 0x6D                | 0x00             | 1                             |

| ELE4, ELE5 Charge Time            |        |        | CDT5              |       |       |         | CDT4  |       |                     | 0x00             |                               |

| ELE6, ELE7 Charge Time            |        |        | CDT7              |       |       | CDT6    |       |       | 0x6F                | 0x00             |                               |

| ELE8, ELE9 Charge Time            |        |        | CDT9              |       |       |         | CDT8  |       | 0x70                | 0x00             | Register<br>Address + 1       |

| ELE10, ELE11 Charge Time          |        |        | CDT11             |       |       |         | CDT10 |       |                     | 0x00             |                               |

| ELEPROX Charge Time               |        |        |                   |       |       | CDTPROX |       |       | 0x72                | 0x00             |                               |

| GPIO Control Register 0           | CTL011 | CTL010 | CTL09             | CTL08 | CTL07 | CTL06   | CTL05 | CTL04 | 0x73                | 0x00             |                               |

| GPIO Control Register 1           | CTL111 | CTL110 | CTL19             | CTL18 | CTL17 | CTL16   | CTL15 | CTL14 | 0x74                | 0x00             |                               |

| GPIO Data Register                | DAT11  | DAT10  | DAT9              | DAT8  | DAT7  | DAT6    | DAT5  | DAT4  | 30x75               | 0x00             |                               |

| GPIO Direction Register           | DIR11  | DIR10  | DIR9              | DIR8  | DIR7  | DIR6    | DIR5  | DIR4  | 0x76                | 0x00             |                               |

| GPIO Enable Register              | EN11   | EN10   | EN9               | EN8   | EN7   | EN6     | EN5   | EN4   | 0x77                | 0x00             |                               |

| GPIO Data Set Register            | SET11  | SET10  | SET9              | SET8  | SET7  | SET6    | SET5  | SET4  | 0x78                | 0x00             |                               |

| GPIO Data Clear Register          | CLR11  | CLR10  | CLR9              | CLR8  | CLR7  | CLR6    | CLR5  | CLR4  | 0x79                | 0x00             |                               |

| GPIO Data Toggle Register         | TOG11  | TOG10  | TOG9              | TOG8  | TOG7  | TOG6    | TOG5  | TOG4  | 0x7A                | 0x00             |                               |

| AUTO-CONFIG Control Register 0    | F      | FI     | RETRY BVA         |       |       |         |       | ACE   | 0x7B                | 0x00             |                               |

| AUTO-CONFIG Control Register 1    | SCTS   |        | OORIE ARFIE ACFIE |       |       |         |       |       | 0x7C                | 0x00             |                               |

| AUTO-CONFIG USL Register          |        | USL    |                   |       |       |         |       |       | 0x7D                | 0x00             | j l                           |

| AUTO-CONFIG LSL Register          | LSL    |        |                   |       |       |         |       |       | 0x7E                | 0x00             |                               |

| AUTO-CONFIG Target Level Register |        |        |                   | T     | L     |         |       |       | 0x7F                | 0x00             | 0x00                          |

| Soft Reset Register               |        |        |                   | SF    | ST    |         |       |       | 0x80                |                  |                               |

# 4 Electrical Characteristics

### 4.1 Absolute Maximum Ratings

Absolute maximum ratings are stress ratings only and functional operation at the maxima is not guaranteed. Stress beyond the limits specified in Table 3 may affect device reliability or cause permanent damage to the device. For functional operating conditions, refer to the remaining tables in this section. This device contains circuitry protecting against damage due to high-static voltage or electrical fields; however, it is advised that normal precautions be taken to avoid application of any voltages higher than maximum-rated voltages to this high-impedance circuit.

| Rating                         | Symbol            | Value                                          | Unit |

|--------------------------------|-------------------|------------------------------------------------|------|

| Supply Voltage                 | V <sub>DD</sub>   | -0.3 to +3.6                                   | V    |

| Supply Voltage                 | V <sub>REG</sub>  | -0.3 to +2.75                                  | V    |

| Input Voltage<br>SCL, SDA, IRQ | V <sub>IN</sub>   | V <sub>SS</sub> - 0.3 to V <sub>DD</sub> + 0.3 | V    |

| Operating Temperature Range    | T <sub>O</sub>    | -40 to +85                                     | °C   |

| GPIO Source Current per Pin    | İ <sub>GPIO</sub> | 12                                             | mA   |

| GPIO Sink Current per Pin      | İ <sub>GPIO</sub> | 1.2                                            | mA   |

| Storage Temperature Range      | T <sub>S</sub>    | -40 to +125                                    | °C   |

### 4.2 ESD and Latch-up Protection Characteristics

Normal handling precautions should be used to avoid exposure to static discharge.

Qualification tests are performed to ensure that these devices can withstand exposure to reasonable levels of static without suffering any permanent damage. During the device qualification, ESD stresses were performed for the Human Body Model (HBM), the Machine Model (MM) and the Charge Device Model (CDM).

A device is defined as a failure if after exposure to ESD pulses, the device no longer meets the device specification. Complete DC parametric and functional testing is performed per the applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

### Table 4. ESD and Latch-up Test Conditions

| Rating                                    | Symbol           | Value | Unit |

|-------------------------------------------|------------------|-------|------|

| Human Body Model (HBM)                    | V <sub>ESD</sub> | ±2000 | V    |

| Machine Model (MM)                        | V <sub>ESD</sub> | ±200  | V    |

| Charge Device Model (CDM)                 | V <sub>ESD</sub> | ±500  | V    |

| Latch-up current at T <sub>A</sub> = 85°C | ILATCH           | ±100  | mA   |

### 4.3 DC Characteristics

This section includes information about power supply requirements and I/O pin characteristics.

### Table 5. DC Characteristics

(Typical Operating Circuit,  $V_{DD}$  and  $V_{REG}$  = 1.8V,  $T_A$  = 25°C, unless otherwise noted.)

| Parameter                                       | Symbol                            | Conditions                                                                                                                                       | Min                   | Тур   | Max                   | Units |

|-------------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------|-----------------------|-------|

| High Supply Voltage                             | V <sub>DD</sub>                   |                                                                                                                                                  | 2.0                   | 3.3   | 3.6                   | V     |

| Low Supply Voltage                              | V <sub>REG</sub>                  |                                                                                                                                                  | 1.71                  | 1.8   | 2.75                  | V     |

|                                                 |                                   | Run Mode @ 1 ms sample period                                                                                                                    |                       | 393   |                       | μA    |

|                                                 | -                                 | Run Mode @ 2 ms sample period                                                                                                                    |                       | 199   |                       | μA    |

|                                                 |                                   | Run Mode @ 4 ms sample period                                                                                                                    |                       | 102   |                       | μA    |

| Average Supply Current <sup>(1)</sup>           | I <sub>DD</sub>                   | Run Mode @ 8 ms sample period                                                                                                                    |                       | 54    |                       | μΑ    |

|                                                 | DD                                | Run Mode @ 16 ms sample period                                                                                                                   |                       | 29    |                       | μΑ    |

|                                                 |                                   | Run Mode @ 32 ms sample period                                                                                                                   |                       | 17    |                       | μΑ    |

|                                                 |                                   | Run Mode @ 64 ms sample period                                                                                                                   |                       | 11    |                       | μΑ    |

|                                                 |                                   | Run Mode @ 128 ms sample period                                                                                                                  |                       | 8     |                       | μΑ    |

| Measurement Supply Current                      | I <sub>DD</sub>                   | Peak of measurement duty cycle                                                                                                                   |                       | 1     |                       | mA    |

| Idle Supply Current                             | I <sub>DD</sub>                   | Stop Mode                                                                                                                                        |                       | 3     |                       | μA    |

| Input Leakage Current ELE_                      | I <sub>IH</sub> , I <sub>IL</sub> |                                                                                                                                                  |                       | 0.025 |                       | μΑ    |

| Input Self-Capacitance on ELE_                  |                                   |                                                                                                                                                  |                       |       | 15                    | pF    |

| Input High Voltage SDA, SCL                     | V <sub>IH</sub>                   |                                                                                                                                                  | 0.7 x V <sub>DD</sub> |       |                       | V     |

| Input Low Voltage SDA, SCL                      | V <sub>IL</sub>                   |                                                                                                                                                  |                       |       | 0.3 x V <sub>DD</sub> | V     |

| Input Leakage Current<br>SDA, SCL               | I <sub>IH</sub> , I <sub>IL</sub> |                                                                                                                                                  |                       | 0.025 | 1                     | μA    |

| Input Capacitance<br>SDA, SCL                   |                                   |                                                                                                                                                  |                       |       | 7                     | pF    |

| Outp <u>ut Lo</u> w Voltage<br>SDA, IRQ         | V <sub>OL</sub>                   | I <sub>OL</sub> = 6mA                                                                                                                            |                       |       | 0.5V                  | V     |

| Output High Voltage<br>ELE4 - ELE11 (GPIO mode) | V <sub>OHGPIO</sub>               | $V_{DD} = 2.7V$ to 3.6V: $I_{OHGPIO} = -10$ mA<br>$V_{DD} = 2.3V$ to 2.7V: $I_{OHGPIO} = -6$ mA<br>$V_{DD} = 1.8V$ to 2.3V: $I_{OHGPIO} = -3$ mA | V <sub>DD</sub> - 0.5 |       |                       | V     |

| Output Low Voltage<br>ELE4 - ELE11 (GPIO mode)  | V <sub>OLGPIO</sub>               | I <sub>OLGPIOD</sub> = 1 mA                                                                                                                      |                       |       | 0.5                   | V     |

| Dower On Decet                                  | V <sub>TLH</sub>                  | V <sub>DD</sub> rising                                                                                                                           | 1.08                  | 1.35  | 1.62                  | V     |

| Power On Reset                                  | V <sub>THL</sub>                  | V <sub>DD</sub> falling                                                                                                                          | 0.88                  | 1.15  | 1.42                  | V     |

1.: ECR set to 0x2C and all 12 channels plus one proximity channel activated. Measurement current CDC is set at maximum of 0x3F.

### 4.4 AC Characteristics

### Table 6. AC Characteristics

(Typical Operating Circuit,  $V_{DD}$  and  $V_{REG}$  = 1.8V,  $T_A$  = 25°C, unless otherwise noted.)

| Parameter                 | Symbol         | Conditions | Min  | Тур | Max  | Units |

|---------------------------|----------------|------------|------|-----|------|-------|

| 8 MHz Internal Oscillator | f <sub>H</sub> |            | 7.44 | 8   | 8.56 | MHz   |

| 1 kHz Internal Oscillator | fL             |            | 0.65 | 1   | 1.35 | kHz   |

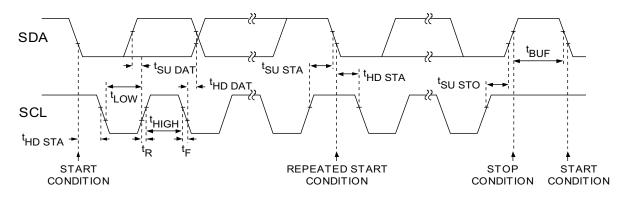

#### I<sup>2</sup>C AC Characteristics 4.5

Table 7. I<sup>2</sup>C AC Characteristics(Typical Operating Circuit,  $V_{DD}$  and  $V_{REG}$  = 1.8V,  $T_A$  = 25°C, unless otherwise noted.)

| Parameter                                          | Symbol               | Conditions | Min | Тур                  | Мах | Units |

|----------------------------------------------------|----------------------|------------|-----|----------------------|-----|-------|

| Serial Clock Frequency                             | f <sub>SCL</sub>     |            |     |                      | 400 | kHz   |

| Bus Free Time Between a STOP and a START Condition | t <sub>BUF</sub>     |            | 1.3 |                      |     | μs    |

| Hold Time, (Repeated) START Condition              | t <sub>HD, STA</sub> |            | 0.6 |                      |     | μs    |

| Repeated START Condition Setup Time                | t <sub>SU, STA</sub> |            | 0.6 |                      |     | μs    |

| STOP Condition Setup Time                          | t <sub>SU, STO</sub> |            | 0.6 |                      |     | μs    |

| Data Hold Time                                     | t <sub>HD, DAT</sub> |            |     |                      | 0.9 | μs    |

| Data Setup Time                                    | t <sub>SU, DAT</sub> |            | 100 |                      |     | ns    |

| SCL Clock Low Period                               | t <sub>LOW</sub>     |            | 1.3 |                      |     | μs    |

| SCL Clock High Period                              | t <sub>HIGH</sub>    |            | 0.7 |                      |     | μs    |

| Rise Time of Both SDA and SCL Signals, Receiving   | t <sub>R</sub>       |            |     | 20+0.1C <sub>b</sub> | 300 | ns    |

| Fall Time of Both SDA and SCL Signals, Receiving   | t <sub>F</sub>       |            |     | 20+0.1C <sub>b</sub> | 300 | ns    |

| Fall Time of SDA Transmitting                      | t <sub>F.TX</sub>    |            |     | 20+0.1C <sub>b</sub> | 250 | ns    |

| Pulse Width of Spike Suppressed                    | t <sub>SP</sub>      |            |     | 25                   |     | ns    |

| Capacitive Load for Each Bus Line                  | Cb                   |            |     |                      | 400 | pF    |

# 5 Register Operation Descriptions

### 5.1 Register Read/Write Operations and Measurement Run/Stop Mode

After power on reset (POR) or soft reset by command, all registers are in reset default initial value (see Table 2). All the registers, except registers 0x5C (default 0x10) and 0x5D (default 0x24), are cleared.

Registers 0x2B ~ 0x7F are control and configuration registers which need to be correctly configured before any capacitance measurement and touch detection.

Registers  $0x00 \sim 0x2A$  are output registers updating periodically by the MPR121 in Run Mode. Among these output registers, Baseline Value Registers  $0x1D \sim 0x2A$  are also writable, this is sometimes useful when user specific baseline values are desired.

The MPR121's Run Mode and Stop Mode are controlled by control bits in Electrode Configuration Register (ECR, 0x5E). When all ELEPROX\_EN and ELE\_EN bits are zeros, the MPR121 is in Stop Mode. While in Stop Mode, there are no capacitance or touch detection measurement on any of the 13 channels. When any of the ELEPROX\_EN and ELE\_EN bits are set to '1', the MPR121 is in Run Mode. The MPR121 will continue to run on its own until it is set again to Stop Mode by the user.

The MPR121 registers read operation can be done at any time, either in Run Mode or in Stop Mode. However, the register write operation can only be done in Stop Mode. The ECR (0x5E) and GPIO/LED control registers (0x73~0x7A) can be written at anytime.

### 5.2 Touch Status Registers (0x00~0x01)

### ELE0-ELE7 Touch Status (0x00)

| Bit   | D7   | D6   | D5   | D4   | D3   | D2   | D1   | D0   |

|-------|------|------|------|------|------|------|------|------|

| Read  | ELE7 | ELE6 | ELE5 | ELE4 | ELE3 | ELE4 | ELE1 | ELE0 |

| Write | _    | —    | _    | _    | _    | _    | _    | _    |

### ELE8-ELE11 ELEPROX Touch Status (0x01)

| Bit   | D7   | D6 | D5 | D4      | D3    | D2    | D1   | D0   |

|-------|------|----|----|---------|-------|-------|------|------|

| Read  | OVCF | _  | _  | ELEPROX | ELE11 | ELE10 | ELE9 | ELE8 |

| Write | —    | _  | _  | _       | _     | _     | _    | _    |

These two registers indicate the detected touch/release status of all of the 13 sensing input channels. ELEPROX is the status for the 13<sup>th</sup> proximity detection channel. The update rate of these status bits will be {ESI x SFI}.

ELEx, ELEPROX: Touch or Release status bit of each respective channel (read only).

1, the respective channel is currently deemed as touched.

0, the respective channel is deemed as released.

**Note:** When an input is not configured as an electrode and enabled as GPIO input port, the corresponding status bit shows the input level, but these GPIO status changes will not cause any IRQ interrupt. This feature is for ELE4~ELE11 only.

OVCF: Over Current Flag (read and write)

1, over current was detected on REXT pin.

0, normal condition.

When over current is detected, the OVCF is set to '1' and the MPR121 goes to Stop Mode. All other bits in status registers 0x00~0x03, output registers 0x04~0x2A, and bits D5~D0 in ECR (0x5E) will also be cleared. When the bit is set at '1', the write to the ECR register to enter Run Mode will be discarded. The write to '1' of the OVCF will clear this bit and the MPR121 fault condition will be cleared. The MPR121 can then be configured to return to the Run Mode again.

### 5.3 Electrode Filtered Data Register (0x04~0x1D)

### Electrode Filtered Data Low Byte (0x04,0x06,...,0x1C)

| Bit   | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read  | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

| Write | —     | —     | _     | —     | _     | _     | —     | —     |

### Electrode Filtered Data High Byte (0x05,0x07,...,0x1D)

| Bit   | D7 | D6 | D5 | D4 | D3 | D2 | D1    | D0    |

|-------|----|----|----|----|----|----|-------|-------|

| Read  | —  | —  | —  | —  | —  | —  | Bit 9 | Bit 8 |

| Write | —  | —  | —  | —  | —  | —  | —     | —     |

The MPR121 provides filtered electrode output data for all 13 channels. The output data is 10-bit and comes from the internal 2nd stage filter output. The data range is 0~1024 or 0x000~0x400 in Hex. Bit 0~7 of the 10-bit data are stored in the low byte and bit 9 and bit 8 are stored in the high byte. The data is the measured voltage on each channel and inversely proportional to the capacitance on that channel.

These registers are read only and are updated every {ESI x SFI}. A multibyte read operation to read both LSB and MSB is recommended to keep the data coherency (i.e, LSB and MSB matching). A multibyte reading of 0x00~0x2A returns results of a single moment without mixing up old and new data.

### 5.4 Baseline Value Register (0x1E~0x2A)

### Electrode Baseline Value (0x1E~0x2A)

| Bit   | D7    | D6    | D5    | D4    | D3    | D2    | D1    | D0    |

|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| Read  | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 |

| Write | DR 0  | DRO   | Dit   | Dir o | BRO   | DR 4  | DRO   | DRE   |

Along with the 10-bit electrode filtered data output, each channel also has a 10-bit baseline value. The update rate of these registers is {ESI x SFI} if baseline tracking operation is enabled. These values are the output of the internal baseline filter operation tracking the slow-voltage variation of the background capacitance change. Touch/release detection is made based on the comparison between the 10-bit electrode filtered data and the 10-bit baseline value.

**Note:** Although internally the baseline value is 10-bit, users can only access the 8 MSB of the 10-bit baseline value through the baseline value registers. The read out from the baseline register must be left shift two bits before comparing it with the 10-bit electrode data.

The Baseline Value register is writable in Stop Mode. Note: when the user writes into the baseline value register, the lower two bits of the 10-bit baseline value are automatically cleared internally upon write operation. The Write to Baseline Value Register by specific values can be sometimes useful if user wants to manipulate the touch/release status. For example, manually setting the target channel from a touch locked state into a touch released state is easily done by setting the baseline value above the signal data.

Refer to the Electrode Configuration Register (ECR, 0x5E) on how to control the on/off operation of baseline tracking and further details on how the initial baseline data is loaded into Run Mode. Refer to Baseline Filtering Control registers(0x2B~0x2A) on how to control the filtering of the baseline value.

### 5.5 Baseline Filtering Control Register (0x2B~0x40)

All12 of the electrode baseline values are controlled by the same set of filtering control registers,  $0x2B \sim 0x35$ . The 13th channel ELEPROX is controlled by registers  $0x36 \sim 0x40$ . Both sets of registers have the same structure using three different scenarios; rising, falling, and touched.

Rising is defined as when the electrode data is greater than the baseline value. Falling is defined as when the electrode data is less than the baseline value. Touched is when the electrode is in touched status. For each scenario, the filtering characteristic is further defined by four parameters: the maximum half delta (MHD), noise half delta (NHD), noise count limit (NCL) and filter delay count limit (FDL). Note: there is no maximum half delta for the touched scenario.

**Maximum Half Delta (MHD):** Determines the largest magnitude of variation to pass through the baseline filter. The range of the effective value is 1~63.

**Noise Half Delta (NHD):** Determines the incremental change when non-noise drift is detected. The range of the effective value is 1~63.

#### MPR121

Noise Count Limit (NCL): Determines the number of samples consecutively greater than the Max Half Delta value. This is necessary to determine that it is not noise. The range of the effective value is 0~255.

Filter Delay Count Limit (FDL): Determines the operation rate of the filter. A larger count limit means the filter delay is operating more slowly. The range of the effective value is 0~255.

The setting of the filter is depended on the actual application. For more information on these registers, refer to application note AN3891.

### 5.6 Touch / Release Threshold (0x41~0x5A)

### ELEx, ELEProx Touch Threshold (0x41,0x43,...,0x59)

| Bit   | D7 | D6    | D5 | D4  | D3 | D2 | D1 | D0 |  |  |  |

|-------|----|-------|----|-----|----|----|----|----|--|--|--|

| Read  |    | ExTTH |    |     |    |    |    |    |  |  |  |

| Write |    |       |    | EXI |    |    |    |    |  |  |  |

### ELEx, ELEProx Release Threshold (0x42,0x44,...,0x5A)

| Bit   | D7 | D6    | D5 | D4  | D3 | D2 | D1 | D0 |  |  |  |

|-------|----|-------|----|-----|----|----|----|----|--|--|--|

| Read  |    | ExRTH |    |     |    |    |    |    |  |  |  |

| Write |    |       |    | EXI |    |    |    |    |  |  |  |

**ExTTH:** Electrode touch threshold, in range of 0~0xFF.

ExRTH: Electrode release threshold, in range of 0~0xFF.

Each of the 13 channels can be set with its own set of touch and release thresholds. Touch and release are detected by comparing the electrode filtered data to the baseline value. The amount of deviation from the baseline value represents a immediate capacitance change detected by possible a touch/release action.

Touch condition: Baseline - Electrode filtered data > Touch threshold

Release condition: Baseline - Electrode filtered data < Release threshold

Threshold settings are dependent on the touch/release signal strength, system sensitivity and noise immunity requirements. In a typical touch detection application, threshold is typically in the range 0x04~0x10. The touch threshold is several counts larger than the release threshold. This is to provide hysteresis and to prevent noise and jitter. For more information, refer to the application note AN3892 and the MPR121 design guidelines.

### 5.7 Debounce Register (0x5B)

### Debounce Register (0x5B)

| Bit   | D7 | D6 | D5  | D4 | D3 | D2 | D1 | D0 |

|-------|----|----|-----|----|----|----|----|----|

| Read  |    |    | DR  |    | _  |    | DT |    |

| Write |    |    | DIX |    |    |    | DT |    |

**DT:** Debounce number for touch. The value range is 0~7.

DR: Debounce number for release. The value range is 0~7.

All 13 channels use the same set of touch and release debounce numbers. The status bits in Status Register 0x00 and 0x01 will only take place after the number of consecutive touch or release detection meets the debounce number setting. The debounce setting can be very useful in avoiding possible noise glitches. Using the debounce setting, the status bit change will have a delay of {ESI x SFI x DR (or DT)}.

## 5.8 Filter and Global CDC CDT Configuration (0x5C, 0x5D)

### Filter/Global CDC Configuration Register (0x5C)

| Bit   | D7 | D6  | D5 | D4  | D3 | D2 | D1 | D0 |  |  |  |

|-------|----|-----|----|-----|----|----|----|----|--|--|--|

| Read  | F  | FFI |    | CDC |    |    |    |    |  |  |  |

| Write |    |     |    | CDC |    |    |    |    |  |  |  |

### Filter/Global CDT Configuration Register (0x5D)

| Bit   | D7 | D6  | D5 | D4 | D3  | D2 | D1  | D0 |  |  |

|-------|----|-----|----|----|-----|----|-----|----|--|--|

| Read  |    | CDT |    | S  | FI  |    | ESI |    |  |  |

| Write |    | CDI |    |    | SFI |    |     |    |  |  |

### **Table 8. Bit Descriptions**

| Field | Description                                                                                                                                                    |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | First Filter Iterations - The first filter iterations field selects the number of samples taken as input to the first level of filtering.                      |

|       | 00 Encoding 0 - Sets samples taken to 6 (Default)                                                                                                              |

| FFI   | 01 Encoding 1 - Sets samples taken to 10                                                                                                                       |

|       | 10 Encoding 2 - Sets samples taken to 18                                                                                                                       |

|       | 11 Encoding 3 - Sets samples taken to 34                                                                                                                       |

|       | Charge Discharge Current - Selects the global value of charge discharge current applied to electrode. The maximum is 63 $\mu$ A, 1 $\mu$ A step.               |

|       | 000000 Encoding 0 - Disable Electrode Charging                                                                                                                 |

| CDC   | 000001 Encoding 1 - Sets the current to 1 μA                                                                                                                   |

| 020   | ~                                                                                                                                                              |

|       | 010000 Encoding 16 - Sets the current to 16 μA (Default)                                                                                                       |

|       | ~<br>111111 Encoding 63 - Sets the current to 63 μA                                                                                                            |

|       | Charge Discharge Time - Selects the global value of charge time applied to electrode.<br>The maximum is 32 $\mu$ s, programmable as 2 $^{(n-2)}$ $\mu$ s.      |

|       | 000 Encoding 0 - Disables Electrode Charging                                                                                                                   |

| CDT   | 001 Encoding 1 - Time is set to 0.5 μs (Default)                                                                                                               |

|       | 010 Encoding 2 - Time is set to 1 μs                                                                                                                           |

|       | ~                                                                                                                                                              |

|       | 111 Encoding 7 - Time is set to 32 μs                                                                                                                          |

|       | Second Filter Iterations - Selects the number of samples taken for the second level filter                                                                     |

|       | 00 Encoding 0 - Number of samples is set to 4 (Default)                                                                                                        |

| SFI   | 01 Encoding 1 - Number of samples is set to 6                                                                                                                  |

|       | 10 Encoding 2 - Number of samples is set to 10                                                                                                                 |

|       | 11 Encoding 3 - Number of samples is set to 18                                                                                                                 |

|       | Electrode Sample Interval - Selects the period between samples used for the second level of filtering. The maximum is 128ms, Programmable to 2 <sup>n</sup> ms |

|       | 000 Encoding 0 - Period set to 1 ms                                                                                                                            |

| ESI   | 001 Encoding 1 - Period set to 2 ms                                                                                                                            |

| 201   | ~                                                                                                                                                              |

|       | 100 Encoding 4 - Period set to 16 ms (Default)                                                                                                                 |

|       | ~                                                                                                                                                              |

|       | 111 Encoding 7 - Period set to 128 ms                                                                                                                          |

These two registers set the global AFE settings. This includes global electrode charge/discharge current CDC, global charge/discharge time CDT, as well as a common filtering setting (FFI, SFI, ESI) for all 13 channels, including the 13th Eleprox channel.

The register 0x5C holds the global CDC and the first level filter configuration for all 13 channels. For each enabled channel, the global CDC will be used for that channel if the respective charge discharge current CDCx setting in 0x5F~0x6B for that channel is zero. If it is not zero, the individual CDCx value will be used in place of the global CDC value. If the MPR121's auto-configuration feature is enabled, CDCx will be automatically set up during system start stage and used for the actual measurement.

The register 0x5D holds the global CDT and the second level filter configuration for all 13 channels. For each enabled channel, the global CDT will be used for that channel if the respective charge discharge time CDTx setting in 0x6C~0x72 for that channel is zero. If it is not zero, the individual CDTx value will be used in place of the global CDT value. If the SCTS bit (Skip Charge Time Search) in the MPR121's autoconfiguration is set, then the current global CDT and CDTx will be used for each channel measurements. If not, then the individual CDTx will be automatically set up during the system start stage and used for the actual measurement.

Using only the global CDC and/or global CDT is acceptable where the capacitance values from all 13 channels are similar. If the electrode pattern, size, or even overlay and base material type changes from one channel to another, then using individual CDCx (and CDTx) will have a better result on sensing sensitivity as each electrode is charged up to a point closing to the supply voltage rail so that the highest sensing field is built for each channel.

The settings for the FFI, SFI, and ESI must be selected according to the system design noise filtering requirement. These settings must also balance the need for power consumption and response time.

When the total time required by scanning and charging/discharge all the enabled channels is longer than the ESI setting, then the actual time will override the ESI setting. For example if the ESI = 4 (16 mS), when FFI = 3 (34 samples), CDT = 7 (32  $\mu$ S), with all 13 channels enabled, the scan time needed is 34 x (32  $\mu$ S + 32  $\mu$ S) x 13 = 28 mS. This 28 mS will be the actual sampling interval instead of ESI (16 mS).

### 5.9 Electrode Charge Current Register (0x5F~0x6B)

### Electrode Charge Current (0x5F~0x6B)

| Bit   | D7 | D6 | D5   | D4   | D3 | D2 | D1 | D0 |  |  |

|-------|----|----|------|------|----|----|----|----|--|--|

| Read  | —  | —  | CDCx |      |    |    |    |    |  |  |

| Write | —  | —  |      | CDCx |    |    |    |    |  |  |

**CDCx:** Sets the charge current applied to each channel. Similar to global CDC value, the range is  $0 \sim 63 \mu$ A, from  $0x00 \sim 0x3F$  in 1  $\mu$ A step. When the CDCx is zero, the global CDC value will be used for that channel.

The individual CDCx bit can either be set manually or automatically (if autoconfiguration is enabled). When the autoconfiguration is enabled, during the first transition from Stop Mode to Run Mode, the system will automatically run a trial search for the appropriate CDCx (and CDTx if SCTS = 0). The individual CDCx will be automatically updated by the MPR121 into the respective registers once autoconfiguration is finished. CDCx is used in the following capacitance measurement and touch detection.

### 5.10 Electrode Charge Time Register (0x6C~0x72)

### Electrode Charge Time (0x6C~0x72)

| Bit   | D7 | D6 | D5     | D4 | D3 | D2 | D1           | D0 |

|-------|----|----|--------|----|----|----|--------------|----|

| Read  | —  |    | CDTx+1 |    | —  |    | CDTx         |    |

| Write | —  |    | ODIXII |    | —  |    | <b>OD</b> TX |    |

**CDTx:** Sets the charge time applied to each channel. Similar to the global CDT value, the range is  $0 \sim 32 \mu$ S, from 2b000~2b111. When the CDTx is zero, the global CDT value is used for that channel.

The individual CDTx bit can be set manually or automatically (if autoconfiguration is enabled). When autoconfiguration is enabled, during the first transition from Stop Mode to Run Mode, the system will automatically run a trial search for the appropriate CDCx (and CDTx if SCST = 0). This means the autoconfiguration will include a search on the CDTx. The individual CDTx will be automatically updated by the MPR121 into the respective registers once the autoconfiguration is finished. This data is used in the following capacitance measurement and touch detection. If SCTS bit is 1, the search on CDTx will be skipped.

### 5.11 Electrode Configuration Register (ECR, 0x5E)

### Electrode Configuration Register (0x5E)

| Bit   | D7 | D6 | D5 | D4         | D3 | D2     | D1 | D0 |  |  |

|-------|----|----|----|------------|----|--------|----|----|--|--|

| Read  | C  | CL |    | ELEPROX_EN |    | ELE_EN |    |    |  |  |

| Write |    |    |    |            |    |        |    |    |  |  |

### Table 9. Bit Descriptions

| Field      | Description                                                                                                                    |

|------------|--------------------------------------------------------------------------------------------------------------------------------|

|            | Calibration Lock - Controls the baseline tracking and how the baseline initial value is loaded                                 |

|            | 00 - Baseline tracking enabled, initial baseline value is current value in baseline value register (Default)                   |

| CL         | 01 - Baseline tracking is disabled                                                                                             |

| -          | 10 - Baseline tracking enabled, initial baseline value is loaded with the 5 high bits of the first 10-bit electrode data value |

|            | 11 - Baseline tracking enabled, initial baseline value is loaded with all 10 bits of the first electrode data value            |

|            | Proximity Enable - Controls the operation of 13th Proximity Detection                                                          |

|            | 00 - Proximity Detection is disabled (Default)                                                                                 |

| ELEPROX_EN | 01 - Run Mode with ELE0~ELE1 combined for proximity detection enabled                                                          |

|            | 10 - Run Mode with ELE0~ELE3 combined for proximity detection enabled                                                          |

|            | 11 - Run Mode with ELE0~ELE11combined for proximity detection enabled                                                          |

|            | Electrode Enable - Controls the operation of 12 electrodes detection                                                           |

|            | 0000 - Electrode detection is disabled (Default)                                                                               |

|            | 0001 - Run Mode with ELE0 for electrode detection enabled                                                                      |

|            | 0010 - Run Mode with ELE0~ ELE1 for electrode detection enabled                                                                |

|            | 0011 - Run Mode with ELE0~ ELE2 for electrode detection enabled                                                                |

|            | 0100 - Run Mode with ELE0~ ELE3 for electrode detection enabled                                                                |

| ELE_EN     | 0101 - Run Mode with ELE0~ ELE4 for electrode detection enabled                                                                |

|            | 0110 - Run Mode with ELE0~ ELE5 for electrode detection enabled                                                                |

|            | 0111 - Run Mode with ELE0~ ELE6 for electrode detection enabled                                                                |

|            | 1000 - Run Mode with ELE0~ ELE7 for electrode detection enabled                                                                |

|            | 1001 - Run Mode with ELE0~ ELE8 for electrode detection enabled                                                                |

|            | 1010 - Run Mode with ELE0~ ELE9 for electrode detection enabled                                                                |

|            | 1011 - Run Mode with ELE0~ ELE10 for electrode detection enabled                                                               |

|            | 11xx - Run Mode with ELE0~ ELE11 for electrode detection enabled                                                               |

The Electrode Configuration Register (ECR) determines if the MPR121 is in Run Mode or Stop Mode, controls the baseline tracking operation and specifies the input configurations of the 13 channels.

The ECR reset default value is 0x00, which means MPR121 is in Stop Mode without capacitance measurement on all 13 channels. Setting ELEPROX\_EN and/or ELE\_EN control bits to non-zero data will put the MPR121 into Run Mode. This will cause the MPR121 to operate immediately on its own. Clearing the ELEPROX\_EN and ELE\_EN all to zeros will set the MPR121 into Stop Mode (which is its lowest power state). The MPR121 can be switched between Stop Mode and Run Mode at anytime by configuring the ECR.

If all channels including the13th proximity detection channel are enabled, the proximity sensing channel is scanned first, followed by ELE0, ELE1..., and ELE11 respectively. The scan runs periodically at the sampling rate specified by the ESI in the Filter/CDT Configuration Register (0x5D). Refer to the table above for configuration of the different channels. Enabling specific channels will save the scan time and sensing field power spent on the unused channels.

In a typical touch detection application, baseline tracking is enabled. This is to compensate for the environment and background induced slow capacitance change to the input sensing channels. The CL bits can enable/disable the baseline tracking and specify how to load the baseline initial values. Since the baseline tracking filtering system has a very large time constant and the initial